### Hitachi 16-Bit Single-Chip Microcomputer

# H8S/2678 Series

H8S/2677 HD64F2677, HD6432677 H8S/2676 HD64F2676, HD6432676 H8S/2675 HD6432675 HBS/2673 HD6432673 HBS/2670 HD6412670

Reference Manual

# **HITACHI**

ADE-602-192A Rev. 2.0 12/5/00 Hitachi, Ltd.

# H8S/2678 Series, H8S/2677 F-ZTAT<sup>TM</sup>, H8S/2676 F-ZTAT<sup>TM</sup> Reference Manual

Publication Date: 1st Edition, March 2000

2nd Edition, December 2000

Published by: Electronic Devices Sales & Marketing Group

Semiconductor & Integrated Circuits

Hitachi, Ltd.

Edited by: Technical Documentation Group

Hitachi Kodaira Semiconductor Co., Ltd.

Copyright © Hitachi, Ltd., 2000. All rights reserved. Printed in Japan.

#### **Cautions**

- Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's

patent, copyright, trademark, or other intellectual property rights for information contained in

this document. Hitachi bears no responsibility for problems that may arise with third party's

rights, including intellectual property rights, in connection with use of the information

contained in this document.

- Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of

- 5. This product is not designed to be radiation resistant.

the Hitachi product.

- 6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- 7. Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.

# Main Revisions and Additions in this Edition

| Page     | Item                       | Revisions (See Manual for Details)                                        |

|----------|----------------------------|---------------------------------------------------------------------------|

| 6        | 1.2 Block Diagram          | Figure 1.1 Internal Block Diagram                                         |

|          |                            | PLLVCC and PLLVSS pins added                                              |

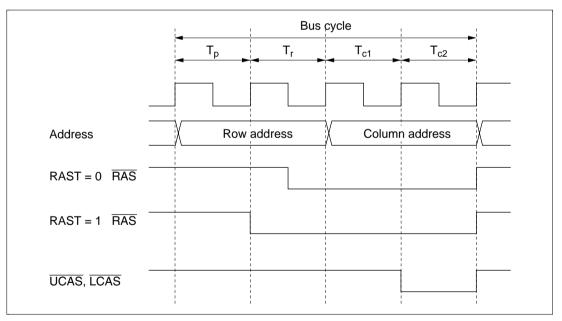

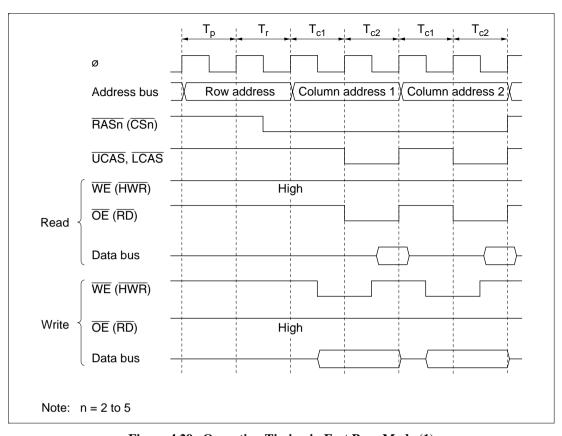

| 151      | 4.5.12 Burst Operation     | Figure 4.29 Operation Timing in Fast Page Mode (1)                        |

|          |                            | Title in parentheses amended                                              |

|          |                            | $CAST = 1 \rightarrow CAST = 0$                                           |

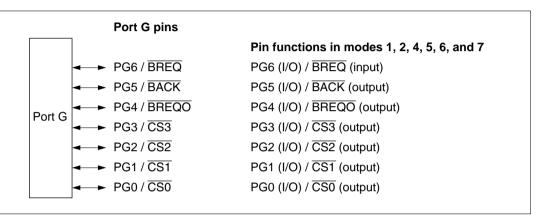

| 286      | 5.16.3 Pin Functions       | Table 5.35 Port G Pin Functions                                           |

|          |                            | PG3 to PG0: Description amended                                           |

| 291      | 5.17.3 Pin Functions       | Table 5.37 Port H Pin Functions                                           |

|          |                            | PH1 and PH0: Description amended                                          |

| 295, 296 | 5.18.1 Port States in Each | Table 5.38 I/O Port States in Each Processing State                       |

|          | Processing State           | PG5 and PG4 states amended                                                |

| 378 to   | 7.1.2 DC Characteristics   | Table 7.2 DC Characteristics                                              |

| 380      |                            | Entire table amended                                                      |

|          |                            | Table 7.3 Permissible Output Currents                                     |

|          |                            | Max. values of $\Sigma I_{\text{OL}}$ and $\Sigma  I_{\text{OH}}$ amended |

| 384      | 7.1.3 AC Characteristics   | Figure 7.3 (2) Oscillation Stabilization Timing added                     |

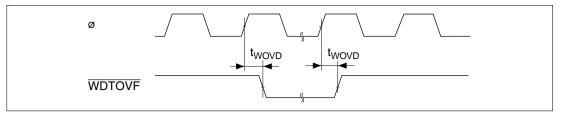

| 414      | -                          | Figure 7.36 WDT Output Timing amended                                     |

| 417      | 7.2.1 Absolute Maximum     | Table 7.11 Absolute Maximum Ratings                                       |

|          | Ratings                    | Note: Operating temperature ranges amended                                |

| 418, 419 | 7.2.2 DC Characteristics   | Table 7.12 DC Characteristics                                             |

|          |                            | Entire table amended                                                      |

| 420      | -                          | Table 7.13 Permissible Output Currents                                    |

|          |                            | Max. values of $\Sigma I_{OL}$ and $\Sigma - I_{OH}$ amended              |

| 432, 433 | 7.2.6 Flash Memory         | Conditions: Operating temperature range amended                           |

|          | Characteristics            | Unit of t <sub>E</sub> amended                                            |

|          |                            | $z$ and $\gamma$ amended                                                  |

# Organization of H8S/2678 Series Reference Manual

The following manuals are available for H8S/2678 Series products.

Table 1 H8S/2678 Series Manuals

| Title                                               | Document Code |

|-----------------------------------------------------|---------------|

| H8S/2600 Series, H8S/2000 Series Programming Manual | ADE-602-083A  |

| H8S/2678 Series Hardware Manual                     | ADE-602-193A  |

| H8S/2678 Series Reference Manual                    | ADE-602-192A  |

The H8S/2600 Series, H8S/2000 Series Programming Manual gives a detailed description of the architecture and instruction set of the H8S/2600 CPU incorporated into H8S/2678 Series products.

The H8S/2678 Series Hardware Manual describes the operation of on-chip functions common to H8S/2678 Series products, and gives a detailed description of the related registers.

The H8S/2678 Series Reference Manual mainly covers information specific to H8S/2678 Series products, including pin arrangement, I/O ports, MCU operating modes (memory maps), interrupt vectors, bus control, and electrical characteristics, and also includes a brief description of all I/O registers for the convenience of the user.

The contents of the H8S/2678 Series Hardware Manual and the H8S/2678 Series Reference Manual are summarized in table 2.

**Table 2** Contents of Hardware Manual and Reference Manual

| No. | Item                                                               | Hardware<br>Manual | Reference<br>Manual                           |

|-----|--------------------------------------------------------------------|--------------------|-----------------------------------------------|

| 1   | Overview                                                           | 0                  | <ul><li>(Including pin arrangement)</li></ul> |

| 2   | MCU operating modes (including memory maps)                        | <del></del>        | 0                                             |

| 3   | Exception handling                                                 | 0                  | 0                                             |

| 4   | Interrupt controller                                               | 0                  | 0                                             |

| 5   | Bus controller                                                     | 0                  | 0                                             |

| 6   | DMA controller (DMAC)                                              | 0                  | <del></del>                                   |

| 7   | Data transfer controller (DTC)                                     | 0                  | _                                             |

| 8   | 16-bit timer unit (TPU)                                            | 0                  | _                                             |

| 9   | Programmable pulse generator (PPG)                                 | 0                  | <del></del>                                   |

| 10  | 8-bit timers                                                       | 0                  | _                                             |

| 11  | Watchdog timer                                                     | 0                  |                                               |

| 12  | Serial communication interface (SCI)                               | 0                  | <del></del>                                   |

| 13  | Smart card interface                                               | 0                  | _                                             |

| 14  | A/D converter                                                      | 0                  |                                               |

| 15  | D/A converter                                                      | 0                  | _                                             |

| 16  | RAM                                                                | 0                  | _                                             |

| 17  | ROM (flash memory)                                                 | 0                  | _                                             |

| 18  | Clock pulse generator                                              | 0                  | _                                             |

| 19  | Power-down modes                                                   | 0                  | _                                             |

| 20  | I/O ports (including port block diagrams)                          | _                  | 0                                             |

| 21  | Electrical characteristics                                         | _                  | 0                                             |

| 22  | Register reference chart (in address order, with function summary) | _                  | 0                                             |

| 23  | Instruction set                                                    | 0                  | _                                             |

| 24  | Package dimension diagrams                                         |                    | 0                                             |

O: Included

©: Included (with detailed register descriptions)

-: Not included

The following chart shows where to find various kinds of information for different purposes.

For product evaluation information, or comparative specification information for current users of Hitachi products

| For H8S/2678 Series specifications |                                      |

|------------------------------------|--------------------------------------|

| Overview                           | 1.1 Overview                         |

| Pin arrangement diagram            | 1.3 Pin Arrangement                  |

| Block diagrams of function modules | Section 6 Peripheral Block Diagrams  |

| Pin functions                      | 1.5 Pin Functions                    |

| Electrical characteristics         | Section 7 Electrical Characteristics |

For detailed information on functions

For use as design material

| For information on H8S/2678 Series registers |          |                                       |  |  |  |  |

|----------------------------------------------|----------|---------------------------------------|--|--|--|--|

| List                                         | <b>_</b> | Section 8 Registers                   |  |  |  |  |

| To find a register from its address          | <b>_</b> | 8.1 List of Registers (Address Order) |  |  |  |  |

| To find register information by function     | <b>_</b> | 8.2 List of Registers (By Module)     |  |  |  |  |

| Setting procedure and notes                  | <b>_</b> | H8S/2678 Series Hardware Manual       |  |  |  |  |

|                                              |          |                                       |  |  |  |  |

| For information on H8S/2678 Series in        | nstruct  | ons                                   |  |  |  |  |

| List                                         |          |                                       |  |  |  |  |

| Operation description and notes              |          | H8S/2600 Series, H8S/2000 Series      |  |  |  |  |

**Programming Manual**

Program examples

# Contents

| Secti | on 1    | Overview                                                       | 1  |

|-------|---------|----------------------------------------------------------------|----|

| 1.1   | Overvio | ew                                                             | 1  |

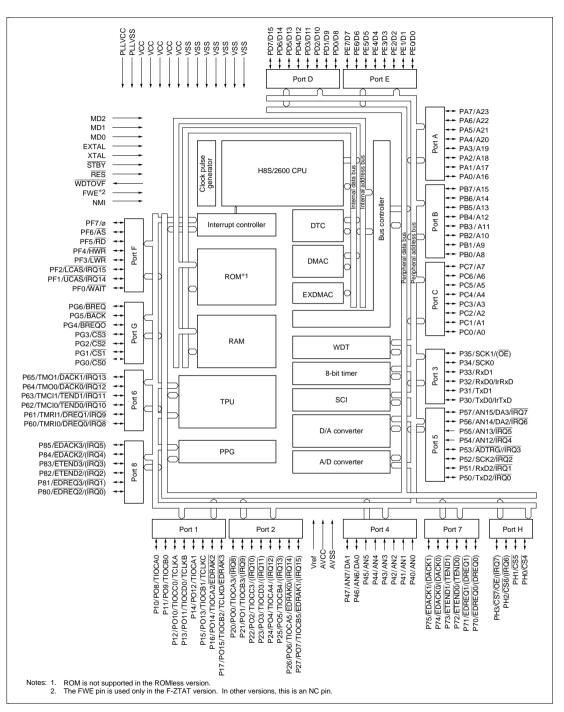

| 1.2   | Block I | Diagram                                                        | 6  |

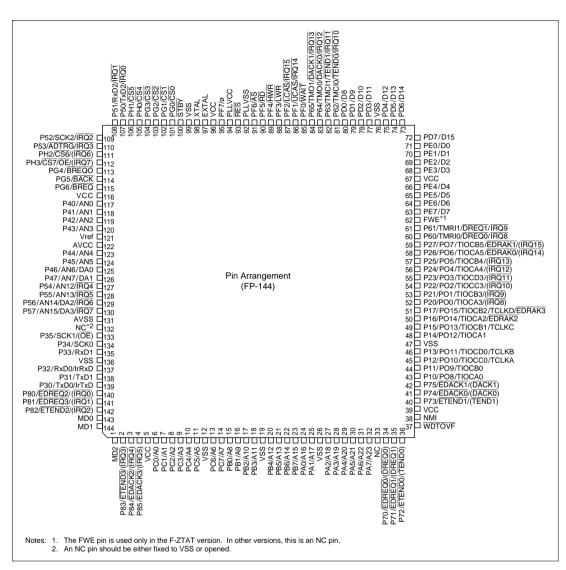

| 1.3   |         | angement                                                       | 7  |

| 1.4   |         | actions in Each Operating Mode                                 | 8  |

| 1.5   | Pin Fur | ections                                                        | 20 |

| 1.6   |         | t Lineup                                                       | 28 |

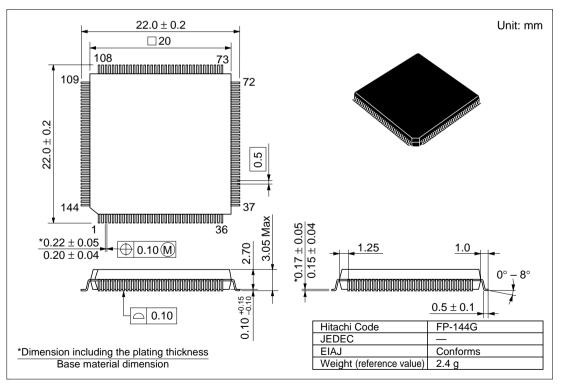

| 1.7   | Packag  | e Dimensions                                                   | 28 |

| Secti | on 2    | MCU Operating Modes                                            | 29 |

| 2.1   |         | ew                                                             | 29 |

| 2.1   | 2.1.1   | Operating Mode Selection (F-ZTAT Version)                      | 29 |

|       | 2.1.2   | Operating Mode Selection (ROMless and Mask ROM Versions)       | 31 |

|       | 2.1.3   | Register Configuration                                         | 33 |

| 2.2   |         | r Descriptions                                                 | 33 |

| 2.2   | 2.2.1   | Mode Control Register (MDCR)                                   | 33 |

|       | 2.2.2   | System Control Register (SYSCR)                                | 34 |

| 2.3   |         | ng Mode Descriptions                                           | 35 |

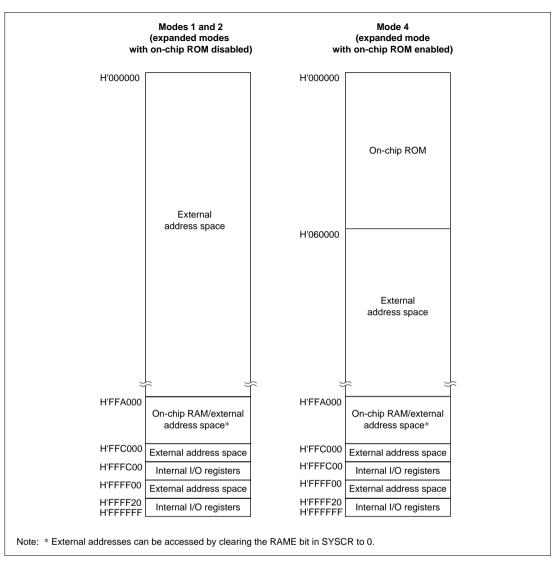

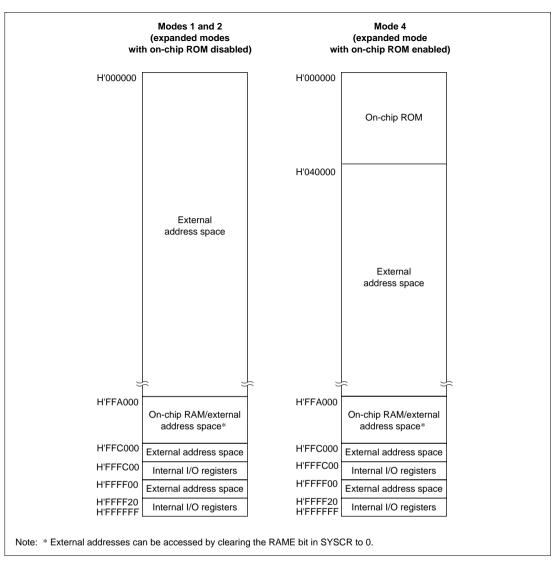

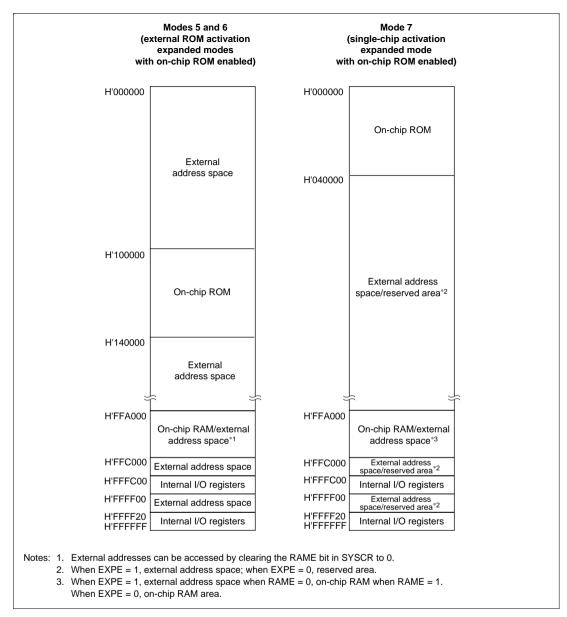

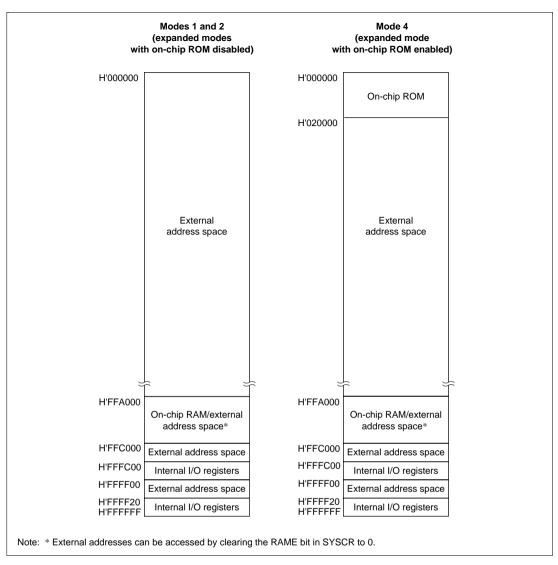

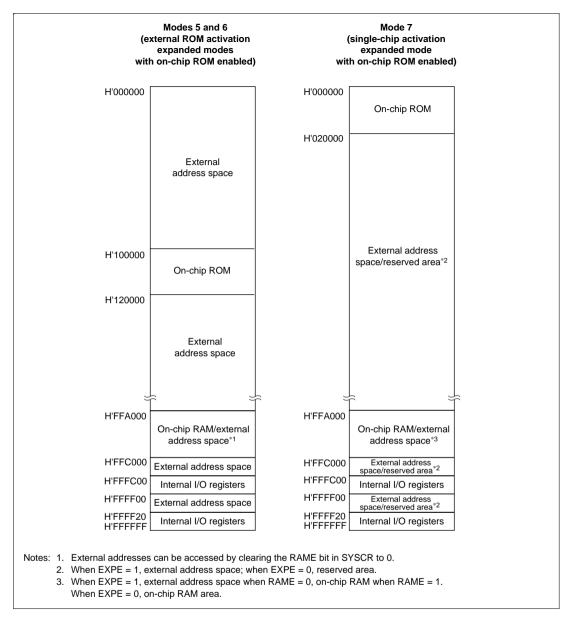

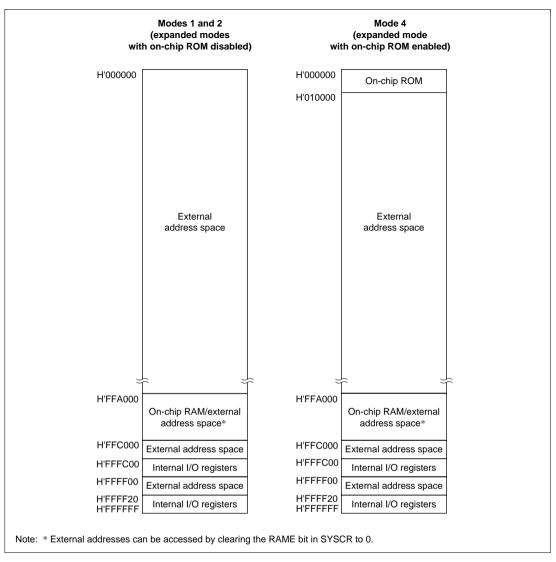

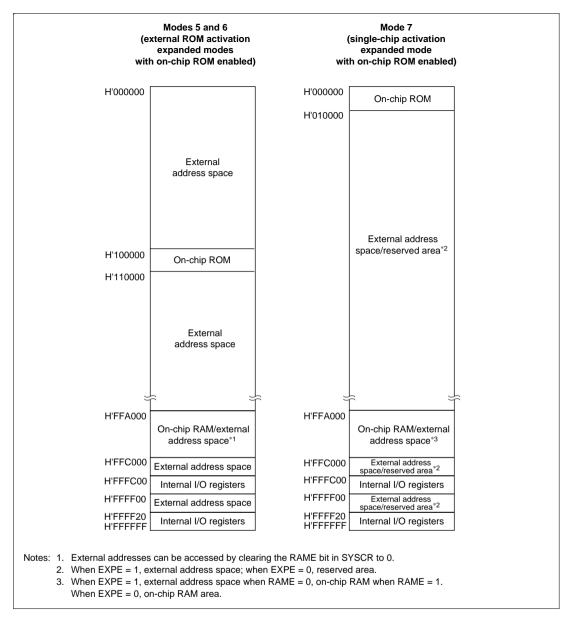

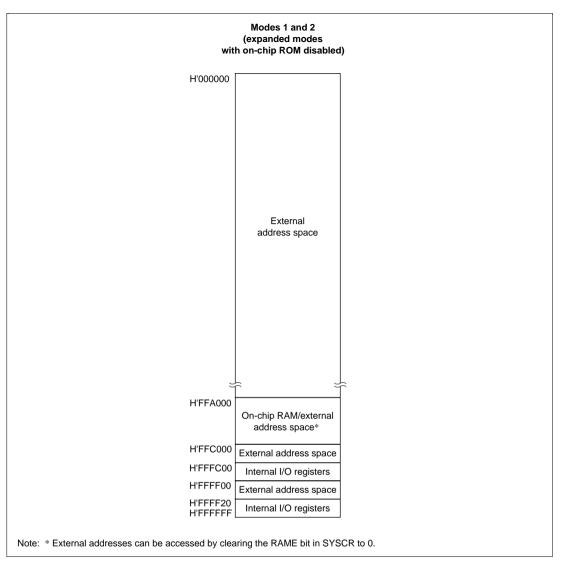

| 2.3   | 2.3.1   | Mode 1 (Expanded Mode with On-Chip ROM Disabled)               | 35 |

|       | 2.3.2   | Mode 2 (Expanded Mode with On-Chip ROM Disabled)               | 35 |

|       | 2.3.3   | Mode 3                                                         | 35 |

|       | 2.3.4   | Mode 4 (Expanded Mode with On-Chip ROM Enabled)                | 36 |

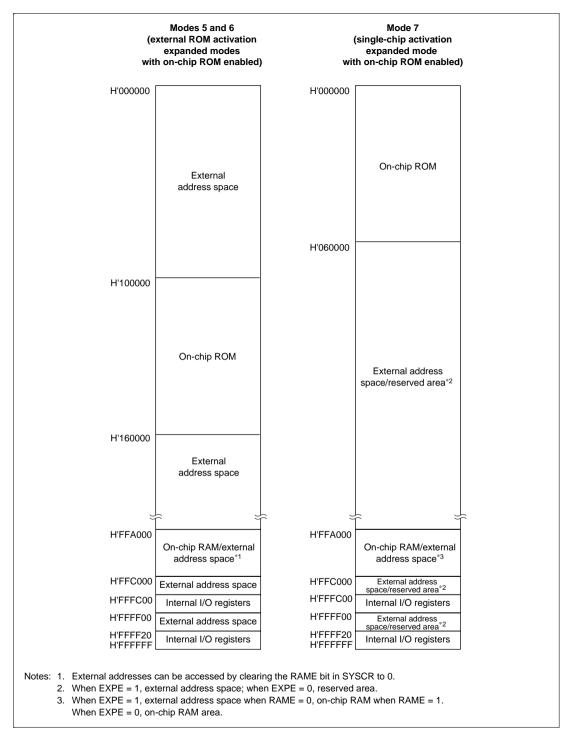

|       | 2.3.5   | Mode 5 (External ROM Activation Expanded Mode with On-Chip ROM | 50 |

|       | 2.0.0   | Enabled)                                                       | 36 |

|       | 2.3.6   | Mode 6 (External ROM Activation Expanded Mode with On-Chip ROM |    |

|       | 2.0.0   | Enabled)                                                       | 36 |

|       | 2.3.7   | Mode 7 (Single-Chip Activation Mode with On-Chip ROM Enabled)  | 36 |

|       | 2.3.8   | Modes 8 and 9 [F-ZTAT Version Only]                            | 37 |

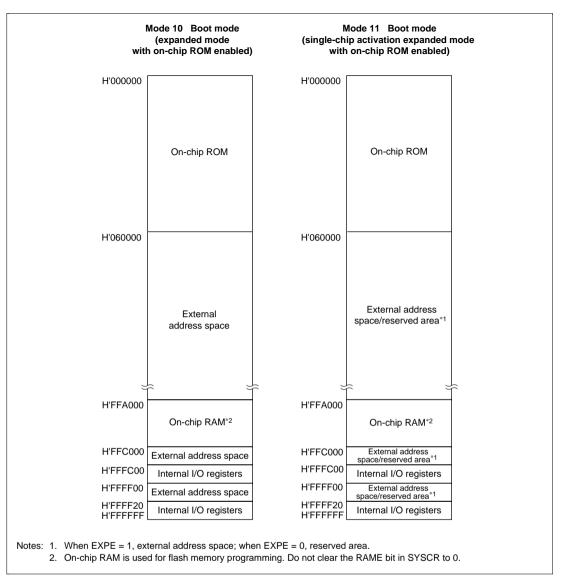

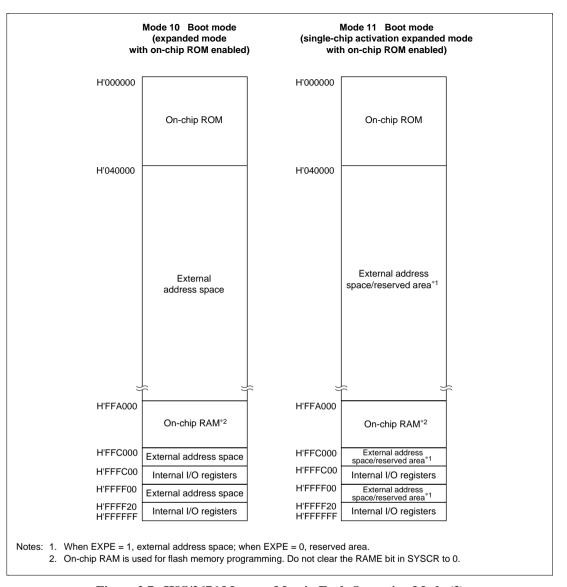

|       | 2.3.9   | Mode 10 [F-ZTAT Version Only]                                  | 37 |

|       | 2.3.10  | Mode 11                                                        | 37 |

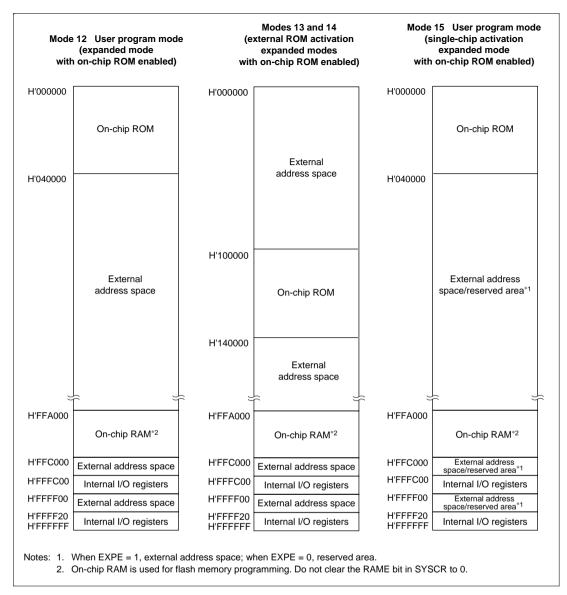

|       | 2.3.11  | Mode 12                                                        | 37 |

|       | 2.3.12  |                                                                | 37 |

|       |         | Mode 15 [F-ZTAT Version Only]                                  | 37 |

| 2.4   |         | actions in Each Operating Mode                                 | 38 |

| 2.5   |         | y Map in Each Operating Mode                                   | 39 |

| Secti | on 3    | Exception Handling and Interrupt Controller                    | 53 |

| 3.1   |         | ew                                                             |    |

| J.1   | 3.1.1   | Exception Handling Types and Priority                          |    |

| 3.2  | mem             | ipi Controllei                                        | J |

|------|-----------------|-------------------------------------------------------|---|

|      | 3.2.1           | Interrupt Controller Features                         | 5 |

|      | 3.2.2           | Block Diagram                                         | 5 |

|      | 3.2.3           | Pin Configuration                                     | 5 |

|      | 3.2.4           | Register Configuration                                | 5 |

| 3.3  | Regist          | er Descriptions                                       | 5 |

|      | 3.3.1           | Interrupt Control Register (INTCR)                    | 5 |

|      | 3.3.2           | Interrupt Priority Registers A to K (IPRA to IPRK)    | 5 |

|      | 3.3.3           | IRQ Enable Register (IER)                             | 6 |

|      | 3.3.4           | IRQ Sense Control Registers H and L (ISCRH, ISCRL)    | 6 |

|      | 3.3.5           | IRQ Status Register (ISR)                             | 6 |

|      | 3.3.6           | IRQ Pin Select Register (ITSR)                        | 6 |

|      | 3.3.7           | Software Standby Release IRQ Enable Register (SSIER)  | 6 |

| 3.4  |                 | ipt Sources                                           | 6 |

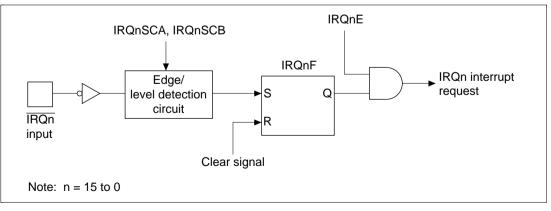

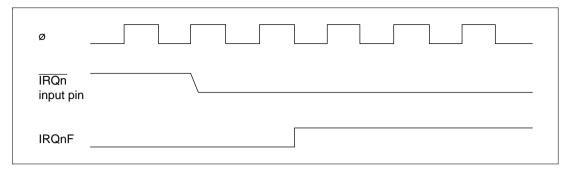

|      | 3.4.1           | External Interrupts                                   | 6 |

|      | 3.4.2           | Internal Interrupts                                   | 6 |

|      | 3.4.3           | Interrupt Vector Table                                | 6 |

| 3.5  |                 | ipt Operation                                         | 7 |

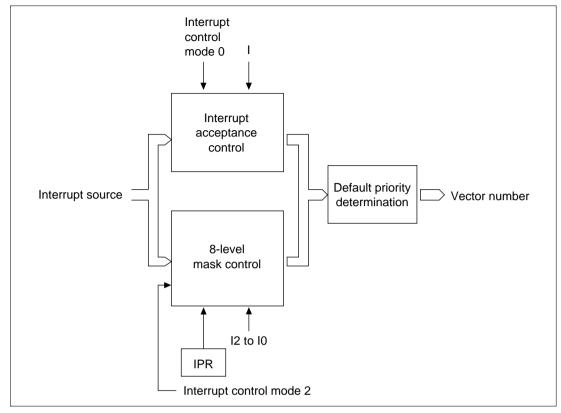

| 0.0  | 3.5.1           | Interrupt Control Modes and Interrupt Operation       | 7 |

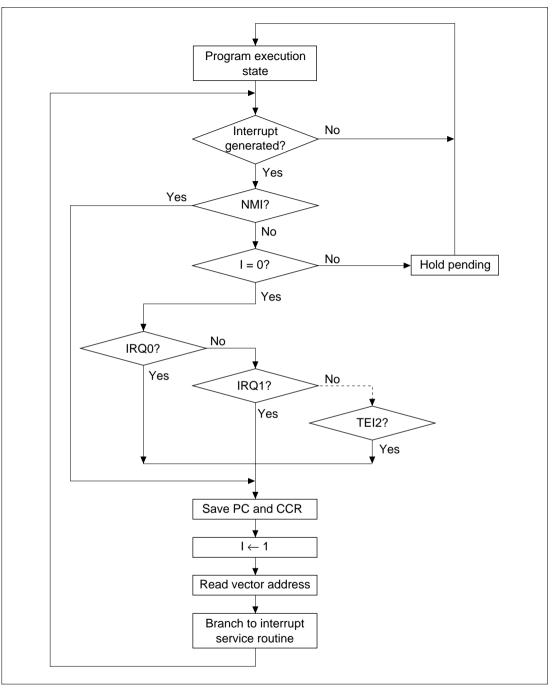

|      | 3.5.2           | Interrupt Control Mode 0                              | 7 |

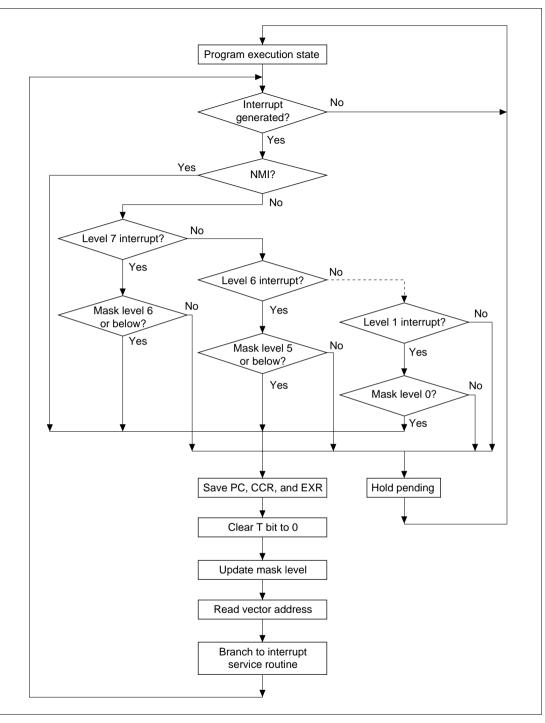

|      | 3.5.3           | Interrupt Control Mode 2                              | 7 |

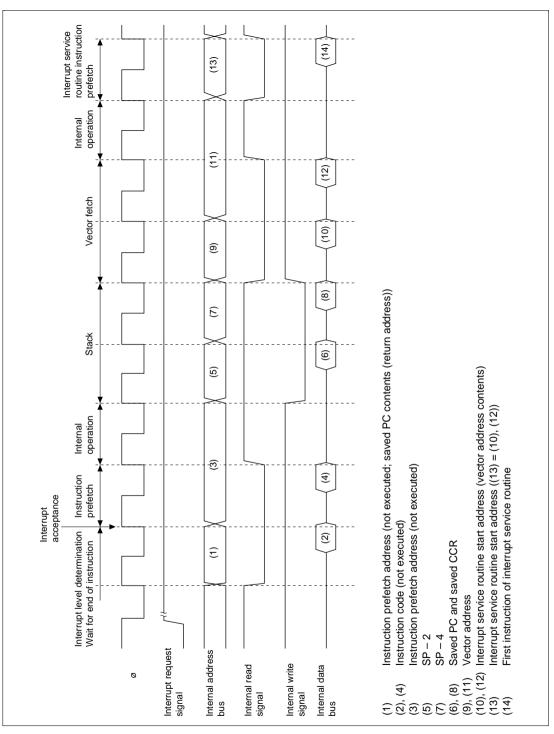

|      | 3.5.4           | Interrupt Exception Handling Sequence                 | 8 |

|      | 3.5.5           | Interrupt Response Times                              | 8 |

| 3.6  |                 | Notes                                                 | 8 |

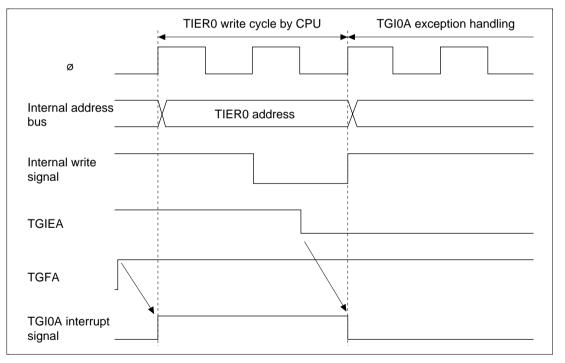

| 5.0  | 3.6.1           | Contention between Interrupt Generation and Disabling | 8 |

|      | 3.6.2           | Instructions that Disable Interrupts                  | 8 |

|      | 3.6.3           | Periods when Interrupts are Disabled                  | 8 |

|      | 3.6.4           | Interrupts during Execution of EEPMOV Instruction     | 8 |

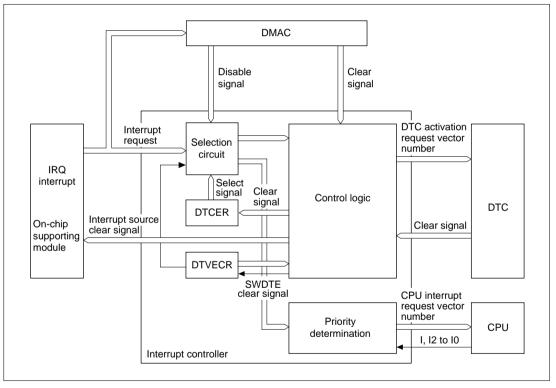

| 3.7  |                 | and DMAC Activation by Interrupt                      | 8 |

| 3.1  | 3.7.1           | Overview                                              | 8 |

|      | 3.7.1           | Block Diagram                                         | 8 |

|      | 3.7.2           | Operation                                             | 8 |

|      | 3.1.3           | Operation                                             | C |

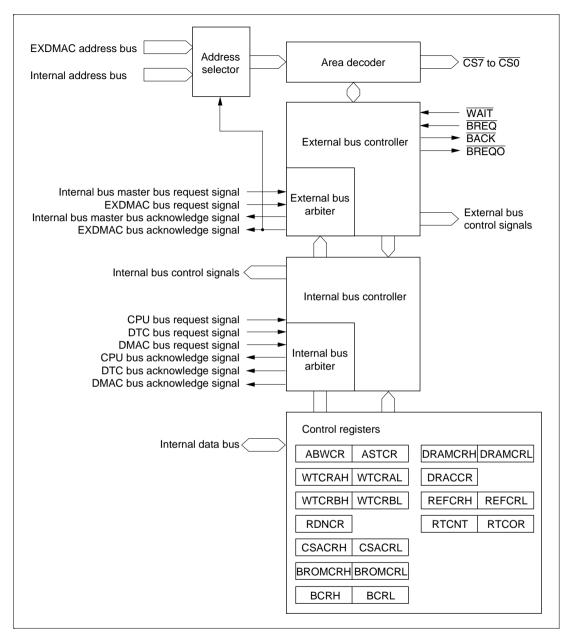

| Sect | ion 4           | Bus Controller                                        | 9 |

| 4.1  |                 | iew                                                   | 9 |

| 7.1  | 4.1.1           | Features                                              | 9 |

|      | 4.1.1           | Block Diagram                                         | 9 |

|      |                 |                                                       |   |

|      | 4.1.3           | Pin Configuration                                     | 9 |

| 4.2  | 4.1.4<br>Pagist | Register Configuration                                | 9 |

| 4.2  | _               | er Descriptions                                       | 9 |

|      | 4.2.1           | Bus Width Control Register (ABWCR)                    | 9 |

|      | 4.2.2           | Access State Control Register (ASTCR)                 | 9 |

|      | 4.2.3           | Wait Control Registers A and B (WTCRA, WTCRB)         | 9 |

| ii   |                 |                                                       |   |

|     | 4.2.4   | Read Strobe Timing Control Register (RDNCR)                     | 99  |

|-----|---------|-----------------------------------------------------------------|-----|

|     | 4.2.5   | CS Assertion Period Control Registers (CSACRH, CSACRL)          | 101 |

|     | 4.2.6   | Area 0 Burst ROM I/F Control Register (BROMCRH)                 |     |

|     |         | Area 1 Burst ROM I/F Control Register (BROMCRL)                 | 103 |

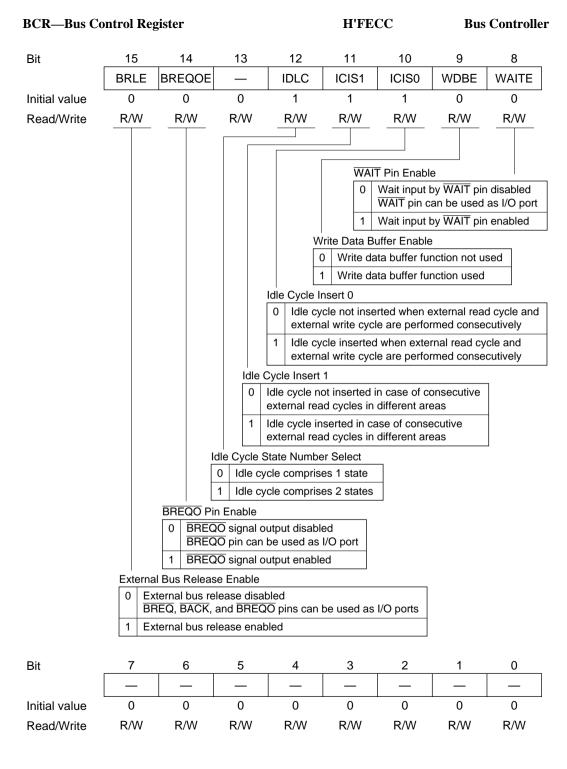

|     | 4.2.7   | Bus Control Register (BCR)                                      | 105 |

|     | 4.2.8   | DRAM Control Register (DRAMCR)                                  | 107 |

|     | 4.2.9   | DRAM Access Control Register (DRACCR)                           | 112 |

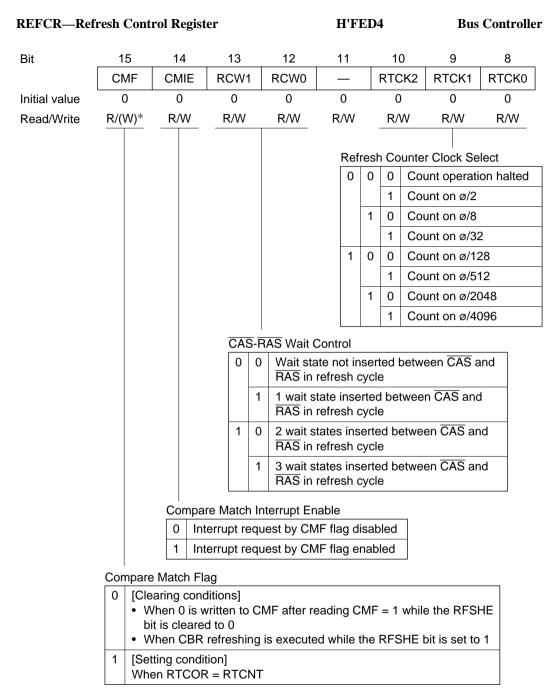

|     | 4.2.10  | Refresh Control Register (REFCR)                                |     |

|     | 4.2.11  | Refresh Timer Counter (RTCNT)                                   |     |

|     | 4.2.12  | Refresh Time Control Register (RTCOR)                           |     |

| 4.3 |         | ew of Bus Control                                               |     |

|     | 4.3.1   | Area Division                                                   | 118 |

|     | 4.3.2   | Bus Specifications                                              |     |

|     | 4.3.3   | Memory Interfaces                                               |     |

|     | 4.3.4   | Chip Select Signals                                             |     |

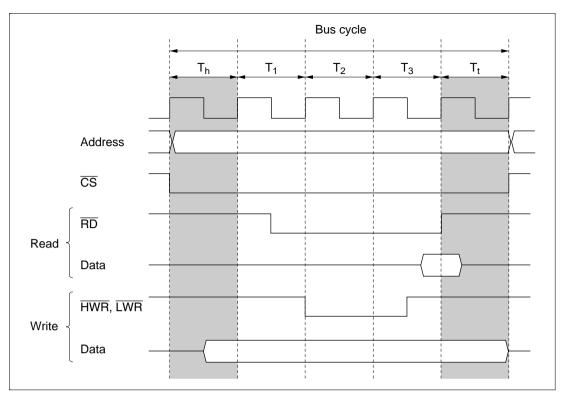

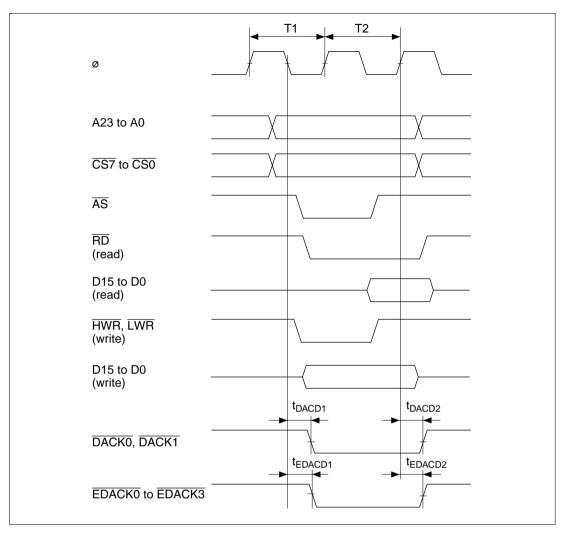

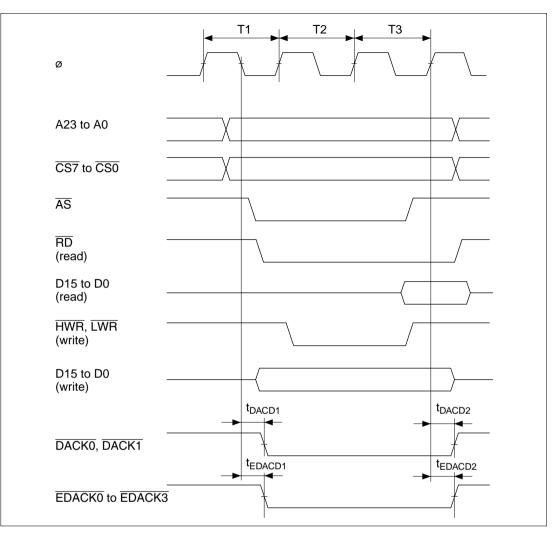

| 4.4 | Basic I | Bus Interface                                                   |     |

|     | 4.4.1   | Overview                                                        |     |

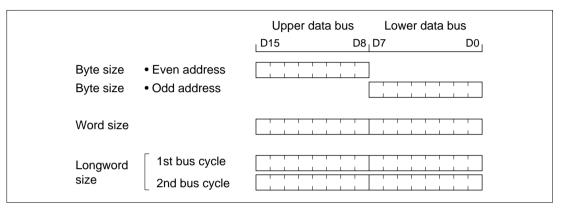

|     | 4.4.2   | Data Size and Data Alignment                                    |     |

|     | 4.4.3   | Valid Strobes                                                   |     |

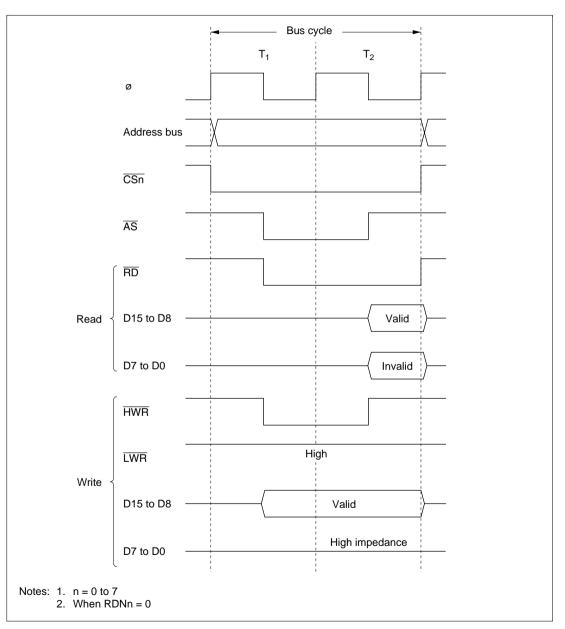

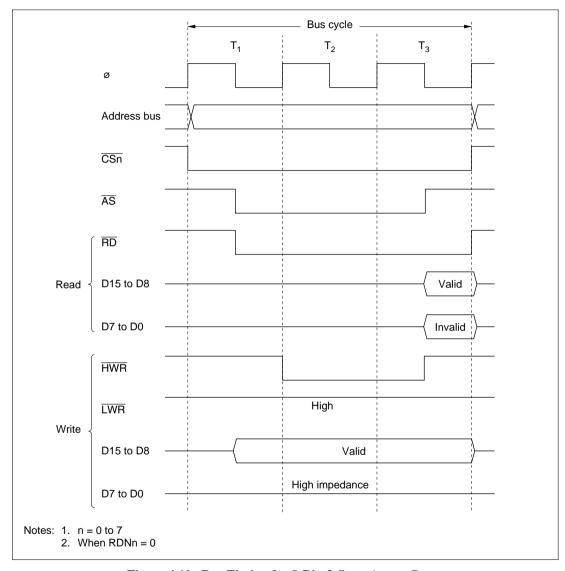

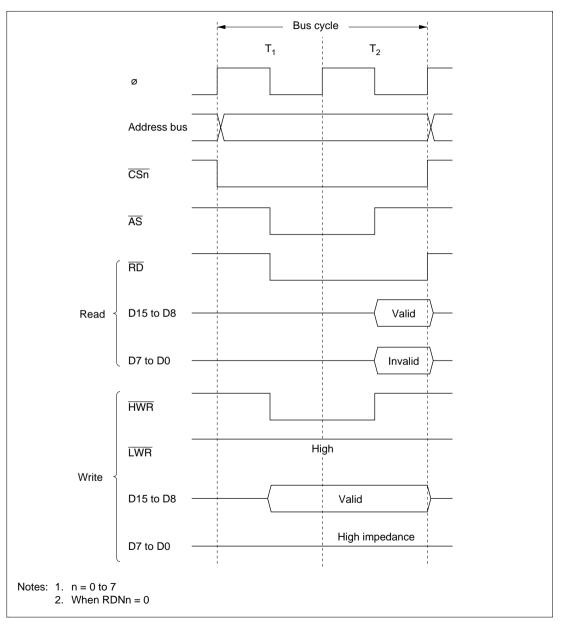

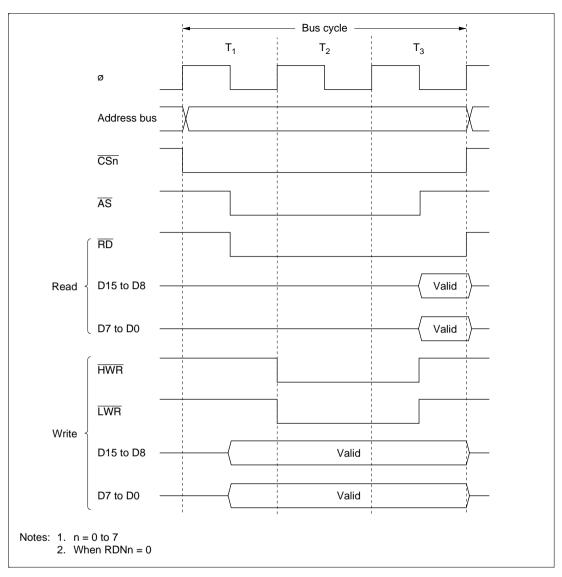

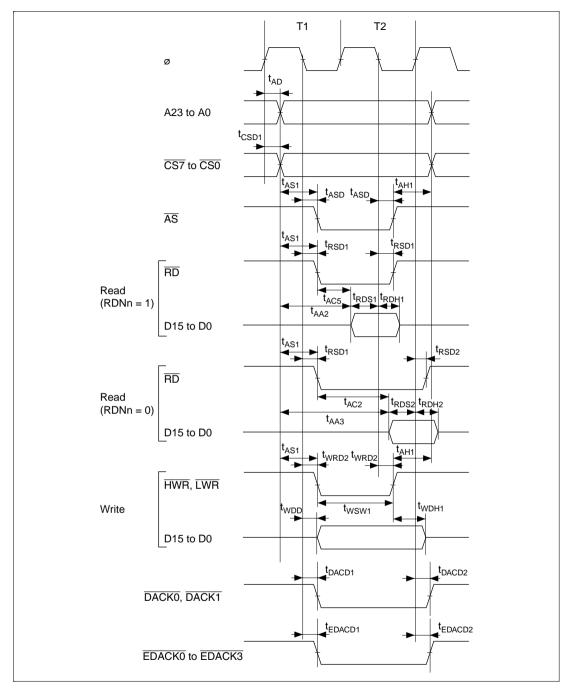

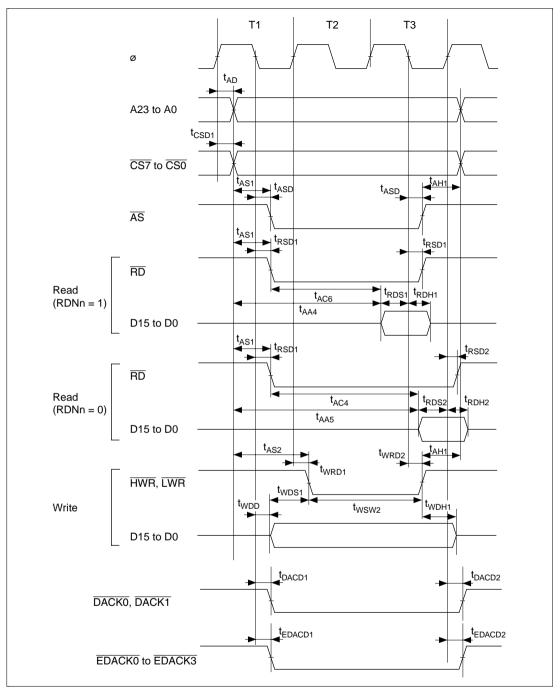

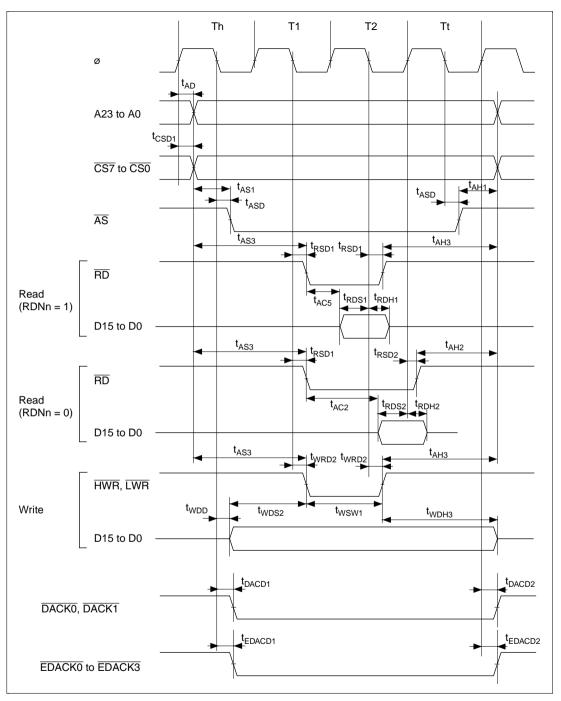

|     | 4.4.4   | Basic Timing.                                                   |     |

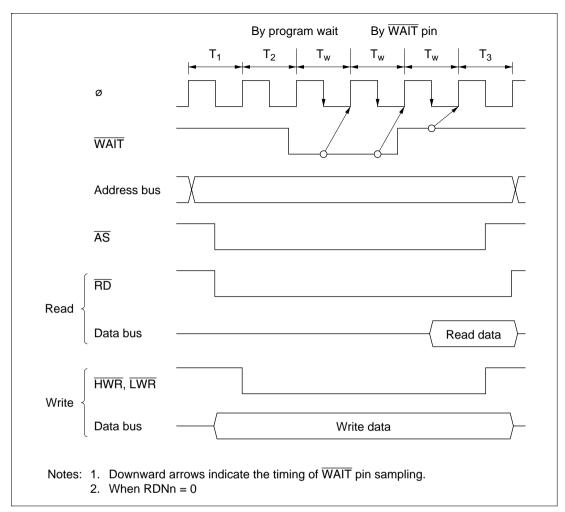

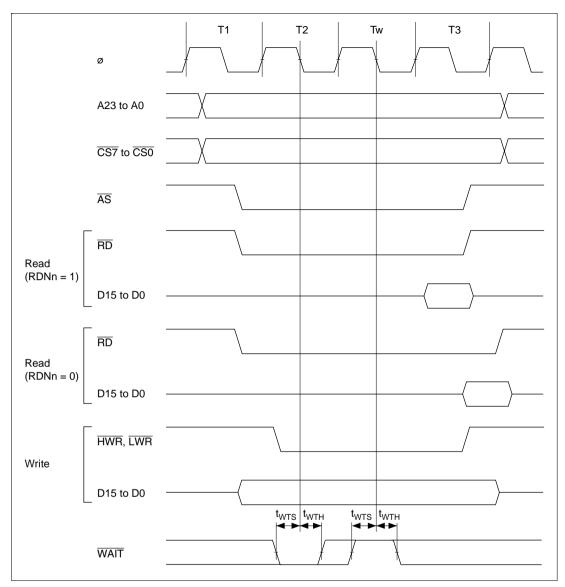

|     | 4.4.5   | Wait Control                                                    |     |

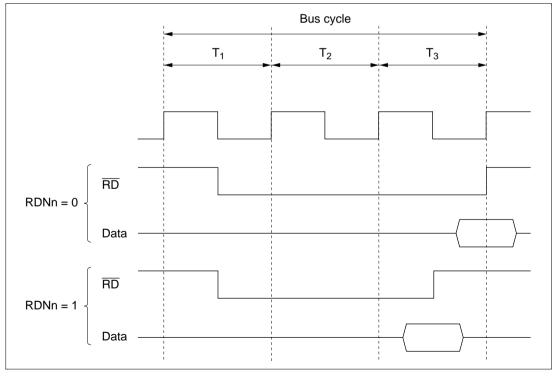

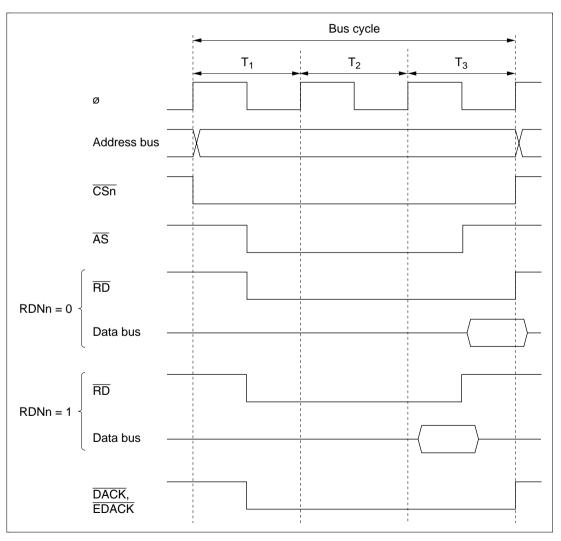

|     | 4.4.6   | Read Strobe (RD) Timing                                         |     |

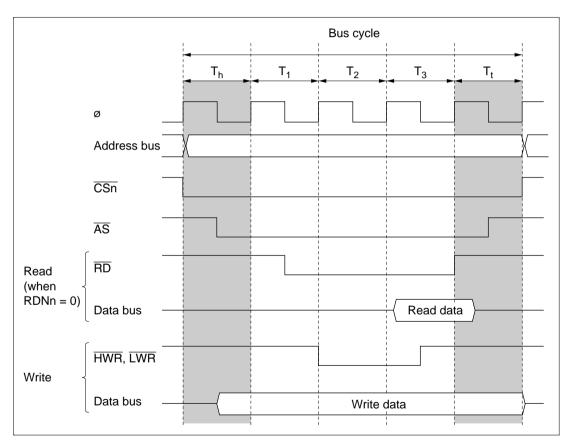

|     | 4.4.7   | Extension of Chip Select (CS) Assertion Period                  |     |

| 4.5 |         | Interface                                                       |     |

|     | 4.5.1   | Overview                                                        |     |

|     | 4.5.2   | Setting DRAM Space                                              |     |

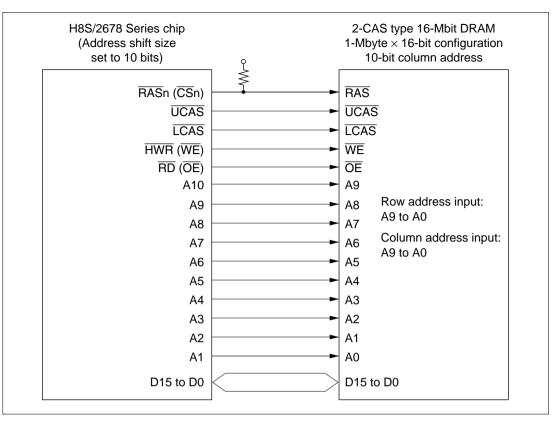

|     | 4.5.3   | Address Multiplexing                                            |     |

|     | 4.5.4   | Data Bus                                                        |     |

|     | 4.5.5   | Pins Used for DRAM Interface                                    |     |

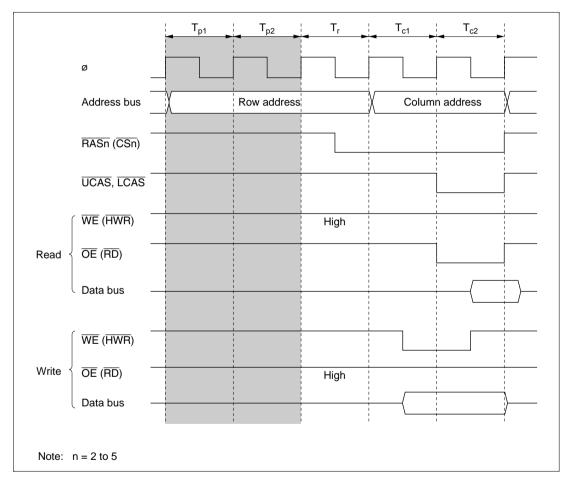

|     | 4.5.6   | Basic Timing                                                    |     |

|     | 4.5.7   | Column Address Output Cycle Control                             |     |

|     | 4.5.8   | Row Address Output Cycle Control                                |     |

|     | 4.5.9   | Precharge State Control                                         |     |

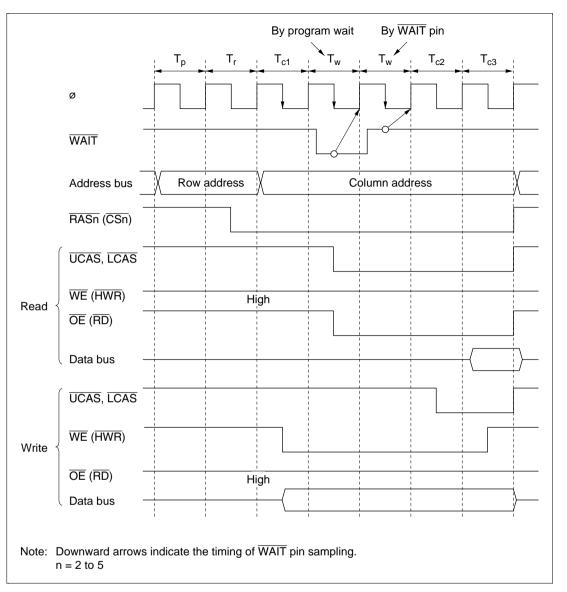

|     | 4.5.10  | Wait Control                                                    |     |

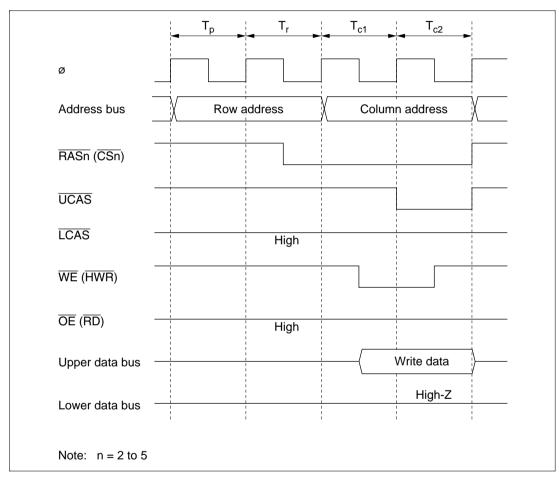

|     |         | Byte Access Control                                             |     |

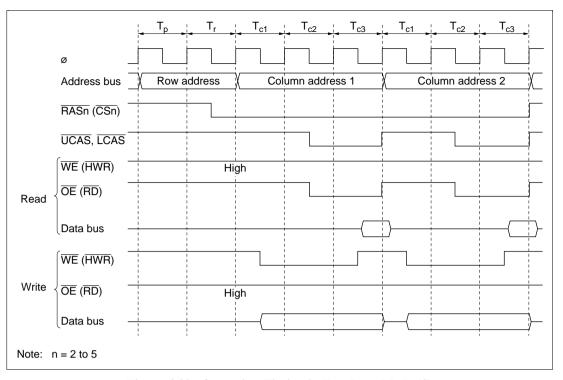

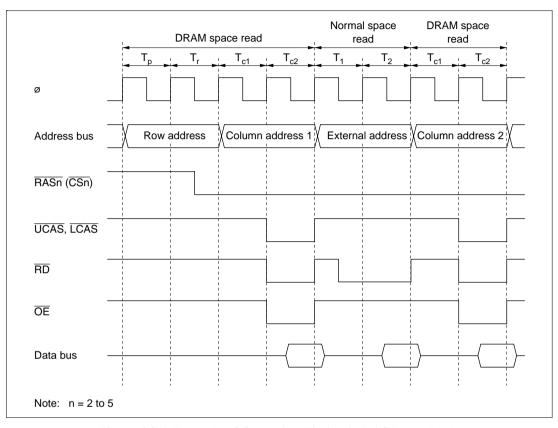

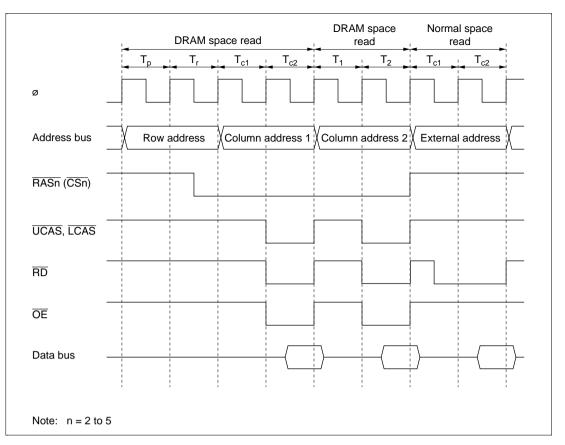

|     |         | Burst Operation                                                 |     |

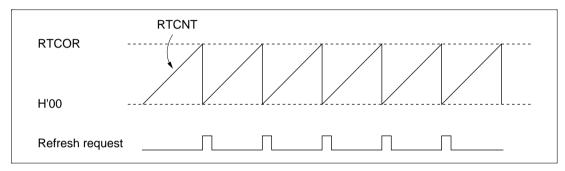

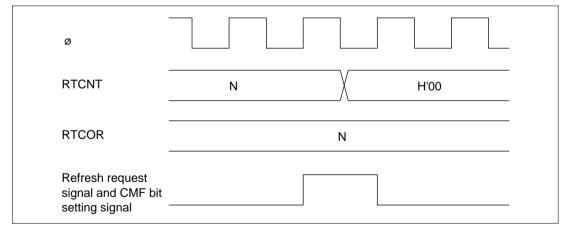

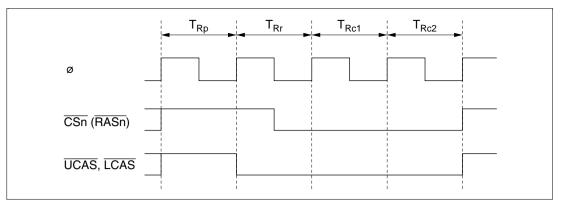

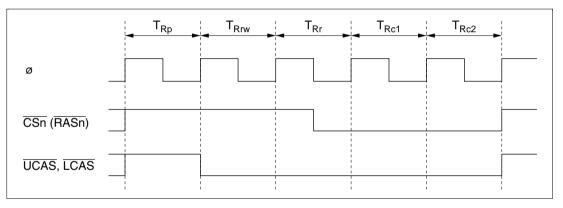

|     | 4.5.13  | Refresh Control.                                                |     |

|     |         | DMAC and EXDMAC Single Address Transfer Mode and DRAM Interface |     |

| 4.6 |         | ROM Interface                                                   |     |

|     | 4.6.1   | Overview                                                        |     |

|     | 4.6.2   | Basic Timing.                                                   |     |

|     | 4.6.3   | Wait Control                                                    |     |

|     | 4.6.4   | Write Access                                                    |     |

|     | 1.0.7   | 1,110 1,100 0,000                                               |     |

|     |         |                                                                 | ii  |

| 4.7   | Idle Cy | cle                                       | 165 |

|-------|---------|-------------------------------------------|-----|

|       | 4.7.1   | Operation                                 | 165 |

|       | 4.7.2   | Pin States in Idle Cycle                  | 173 |

| 4.8   | Write I | Data Buffer Function                      | 173 |

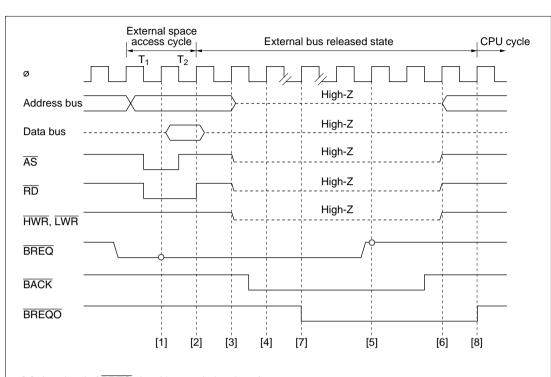

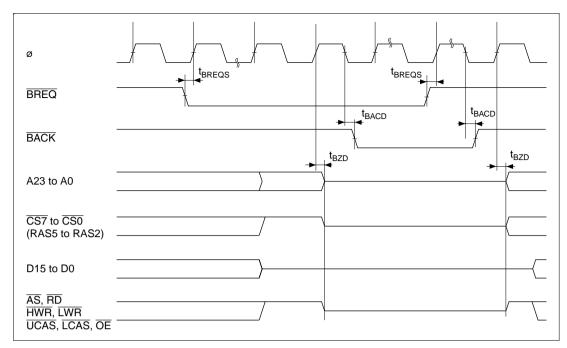

| 4.9   | Bus Re  | lease                                     | 174 |

|       | 4.9.1   | Overview                                  | 174 |

|       | 4.9.2   | Operation                                 | 175 |

|       | 4.9.3   | Pin States in External Bus Released State | 176 |

|       | 4.9.4   | Transition Timing                         | 177 |

|       | 4.9.5   | Usage Notes                               | 178 |

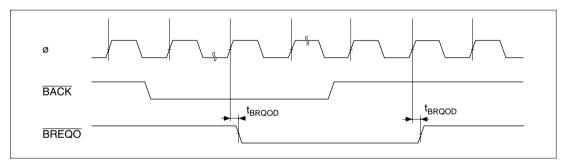

| 4.10  | Bus Ar  | bitration                                 | 179 |

|       | 4.10.1  | Overview                                  | 179 |

|       | 4.10.2  | Operation                                 | 179 |

|       | 4.10.3  | Bus Transfer Timing                       | 180 |

| 4.11  | Bus Co  | ontroller Operation in a Reset            | 181 |

|       |         |                                           |     |

| Secti | ion 5   | I/O Ports                                 | 183 |

| 5.1   | Overvi  | ew                                        | 183 |

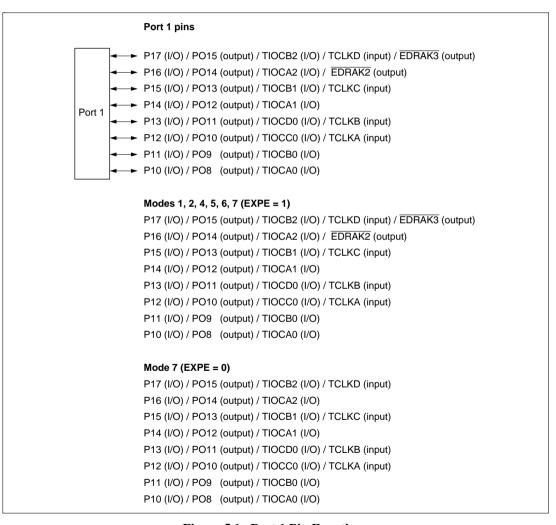

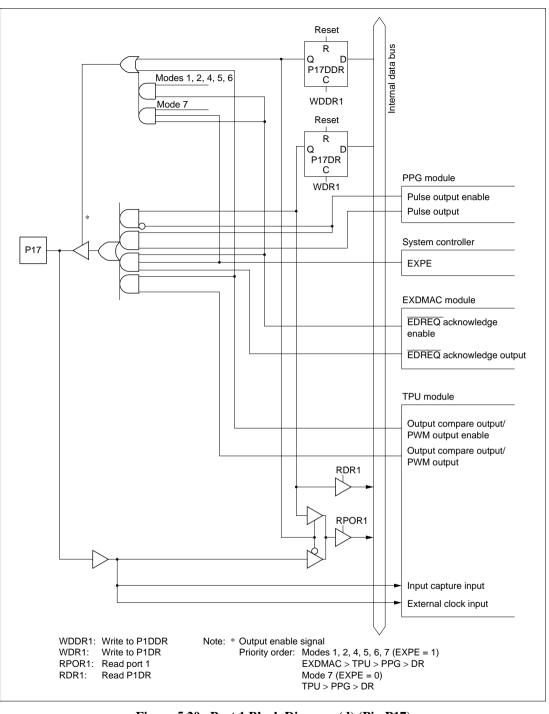

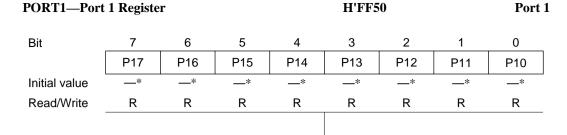

| 5.2   | Port 1. |                                           | 192 |

|       | 5.2.1   | Overview                                  | 192 |

|       | 5.2.2   | Register Configuration                    | 193 |

|       | 5.2.3   | Pin Functions                             | 194 |

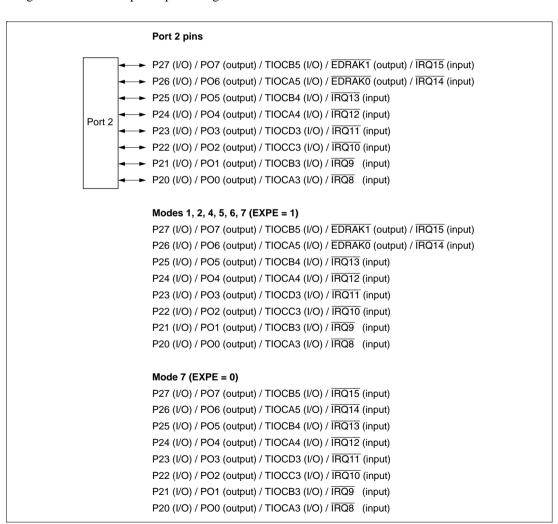

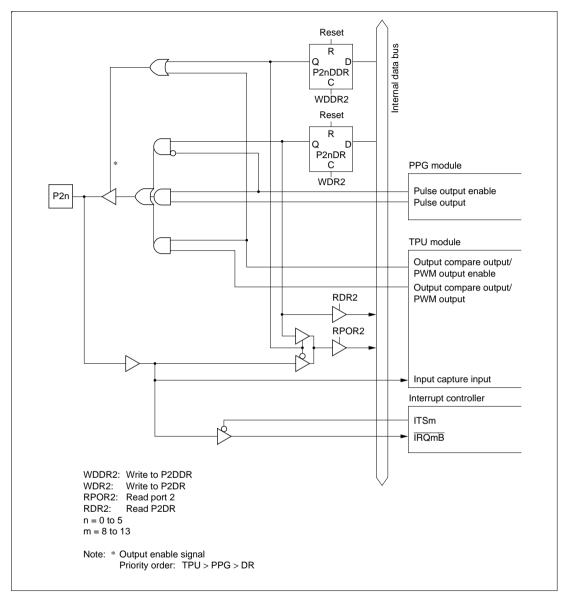

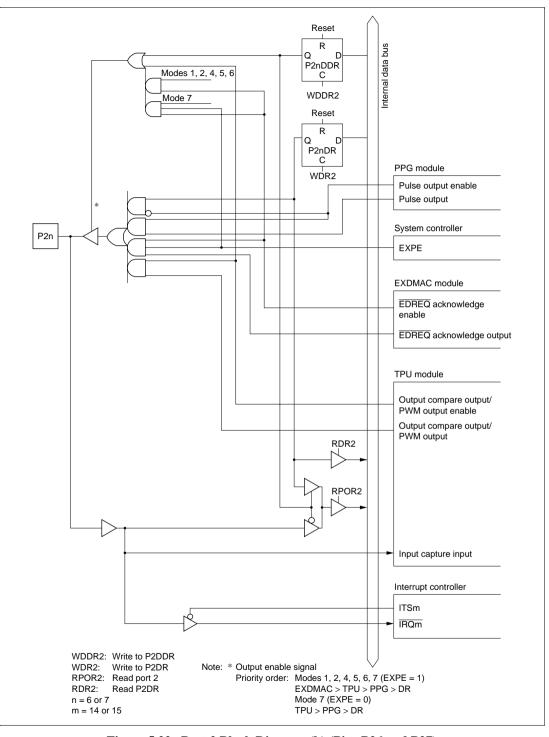

| 5.3   | Port 2. |                                           | 203 |

|       | 5.3.1   | Overview                                  |     |

|       | 5.3.2   | Register Configuration                    |     |

|       | 5.3.3   | Pin Functions                             |     |

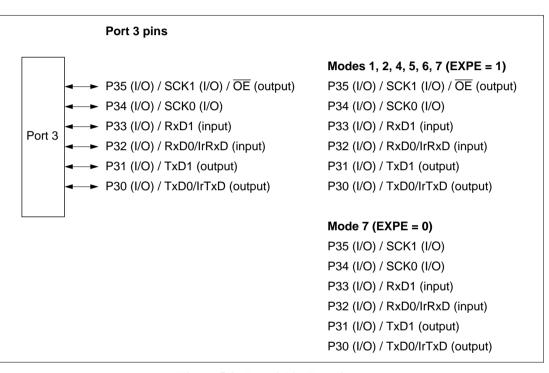

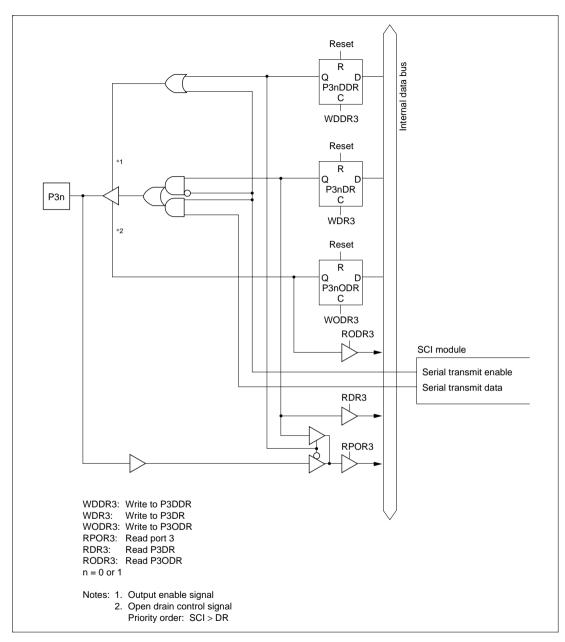

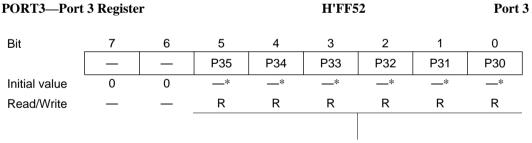

| 5.4   | Port 3. |                                           |     |

|       | 5.4.1   | Overview                                  |     |

|       | 5.4.2   | Register Configuration                    |     |

|       | 5.4.3   | Pin Functions                             | 217 |

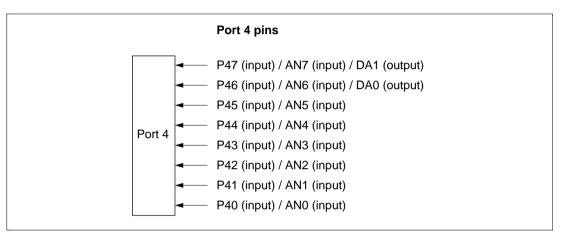

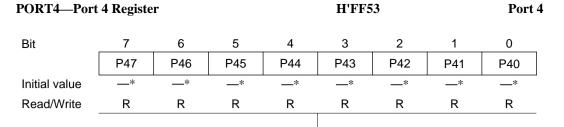

| 5.5   | Port 4. |                                           |     |

|       | 5.5.1   | Overview                                  |     |

|       | 5.5.2   | Register Configuration                    |     |

|       | 5.5.3   | Pin Functions                             |     |

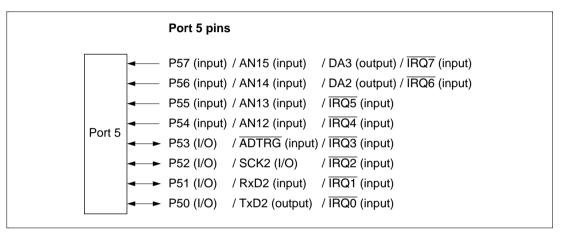

| 5.6   | Port 5. |                                           | 222 |

|       | 5.6.1   | Overview                                  |     |

|       | 5.6.2   | Register Configuration                    |     |

|       | 5.6.3   | Pin Functions                             |     |

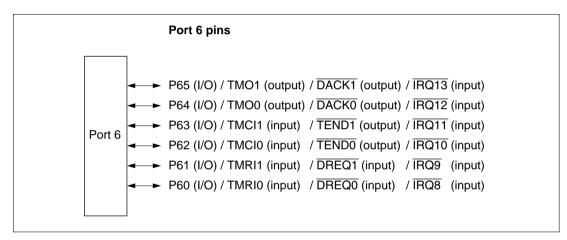

| 5.7   |         |                                           |     |

|       | 5.7.1   | Overview                                  | 227 |

|       | 5.7.2   | Register Configuration                    | 227 |

|       | 5.7.3   | Pin Functions                             |     |

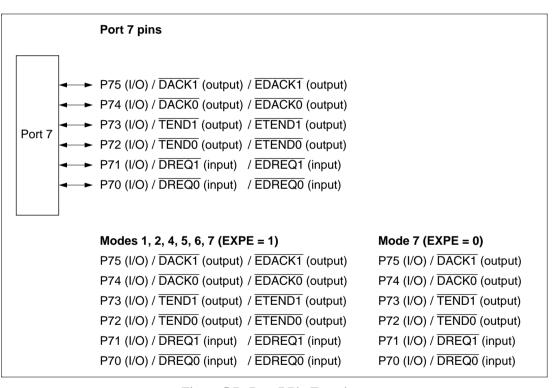

| 5.8   | Port 7. |                                           | 233 |

| iv    |         |                                           |     |

|       |         | HITACHI                                   |     |

|      | 3.6.1   | Overview                   | 23. |

|------|---------|----------------------------|-----|

|      | 5.8.2   | Register Configuration     | 234 |

|      | 5.8.3   | Pin Functions              | 236 |

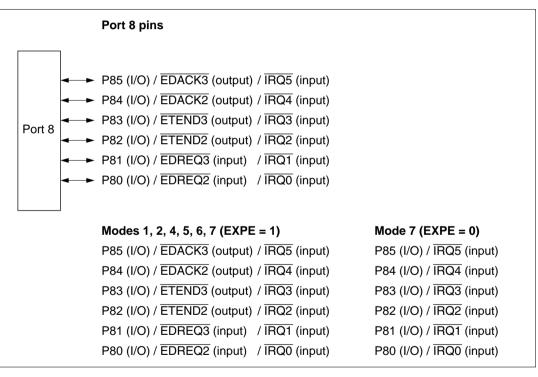

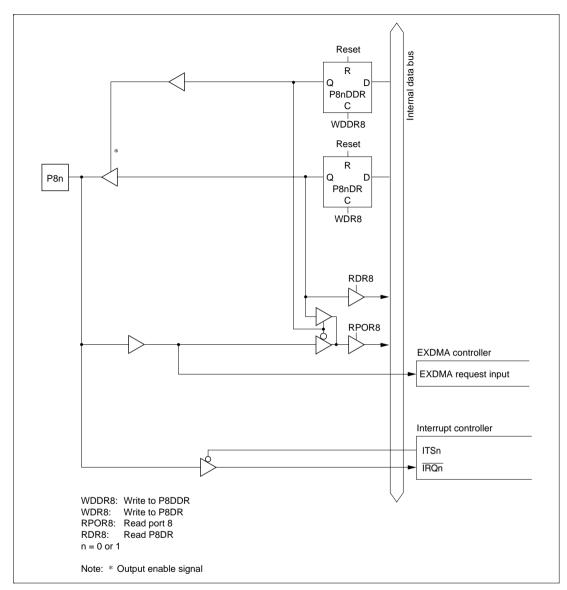

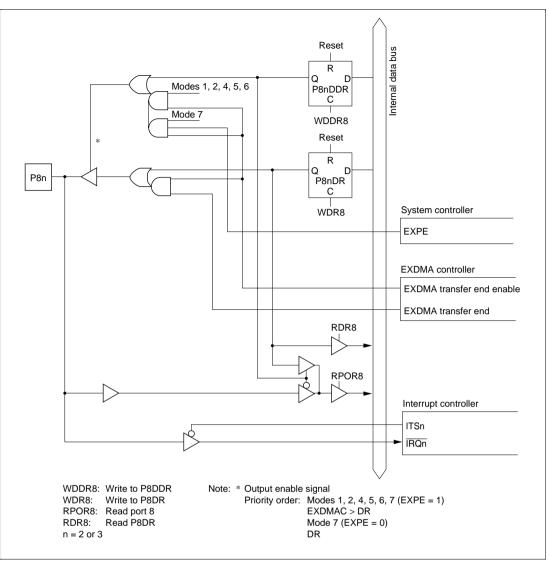

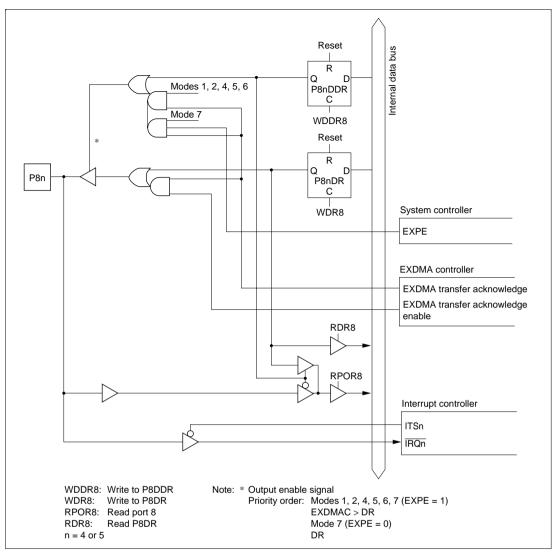

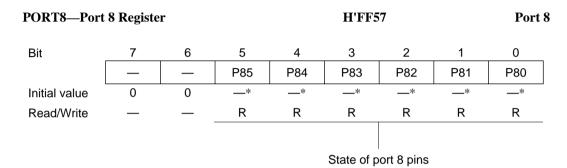

| 5.9  | Port 8. |                            | 240 |

|      | 5.9.1   | Overview                   | 240 |

|      | 5.9.2   | Register Configuration     | 24  |

|      | 5.9.3   | Pin Functions              |     |

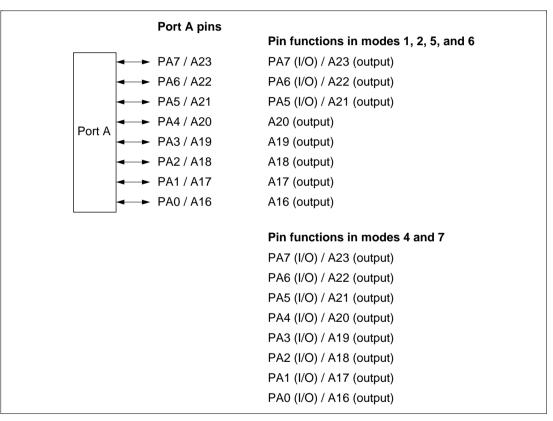

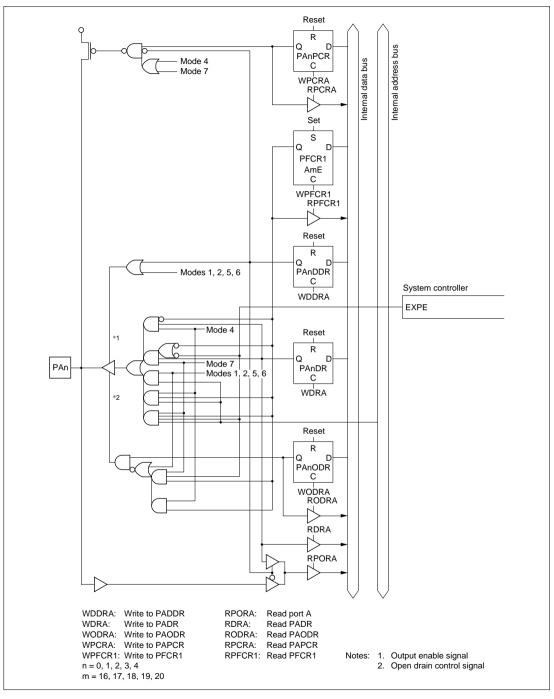

| 5.10 | Port A. |                            |     |

|      | 5.10.1  | Overview                   | 240 |

|      | 5.10.2  |                            |     |

|      | 5.10.3  |                            |     |

|      | 5.10.4  | MOS Input Pull-Up Function |     |

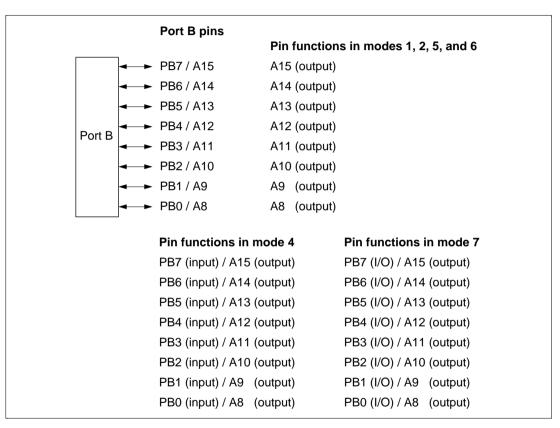

| 5.11 |         |                            |     |

|      |         | Overview                   |     |

|      | 5.11.2  |                            |     |

|      | 5.11.3  |                            |     |

|      | 5.11.4  | MOS Input Pull-Up Function |     |

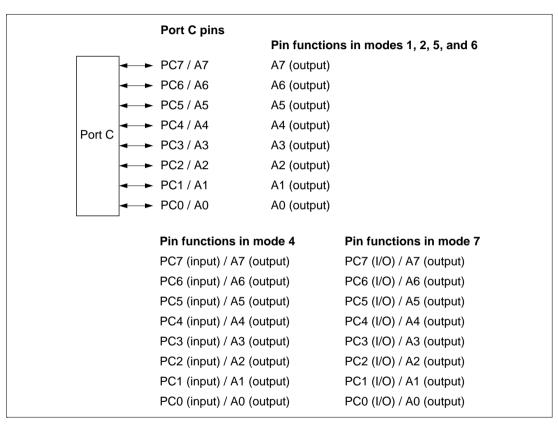

| 5.12 |         |                            |     |

|      |         | Overview                   |     |

|      |         | Register Configuration     |     |

|      |         | Pin Functions              |     |

|      |         | MOS Input Pull-Up Function |     |

| 5.13 |         |                            |     |

|      |         | Overview                   |     |

|      |         | Register Configuration     |     |

|      |         | Pin Functions              |     |

|      |         | MOS Input Pull-Up Function |     |

| 5.14 |         | opp                        |     |

|      |         | Overview                   |     |

|      |         | Register Configuration     |     |

|      |         | Pin Functions              |     |

|      |         | MOS Input Pull-Up Function |     |

| 5.15 |         | obpu un op . unvus.        |     |

|      |         | Overview                   |     |

|      |         | Register Configuration     |     |

|      |         | Pin Functions              |     |

| 5.16 |         |                            |     |

|      | 5.16.1  | Overview                   |     |

|      | 5.16.2  |                            |     |

|      |         | Pin Functions              |     |

| 5.17 |         | 1 III 1 dilections         |     |

| ,    |         | Overview                   |     |

|      |         | Register Configuration     |     |

|      | 2.17.2  | o                          |     |

|      |         |                            | ,   |

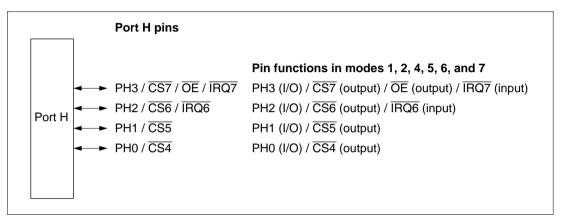

|      | 5.17.3   | Pin Functions                        | 290 |

|------|----------|--------------------------------------|-----|

| 5.18 | Pin Fun  | ctions                               | 292 |

|      | 5.18.1   | Port States in Each Processing State | 292 |

| 5.19 | I/O Por  | t Block Diagrams                     | 297 |

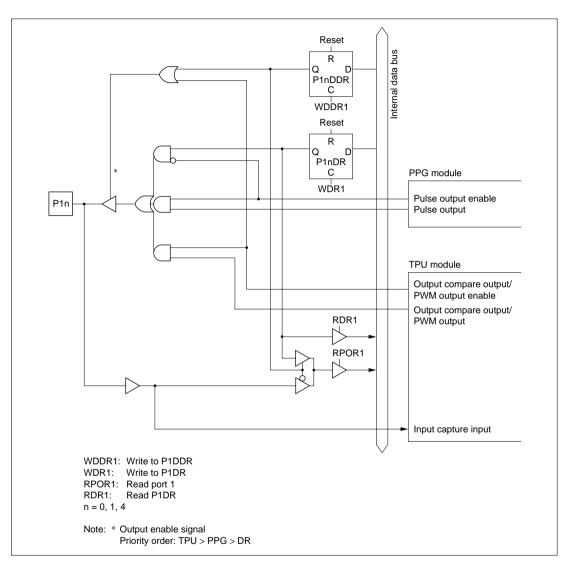

|      | 5.19.1   | Port 1                               | 297 |

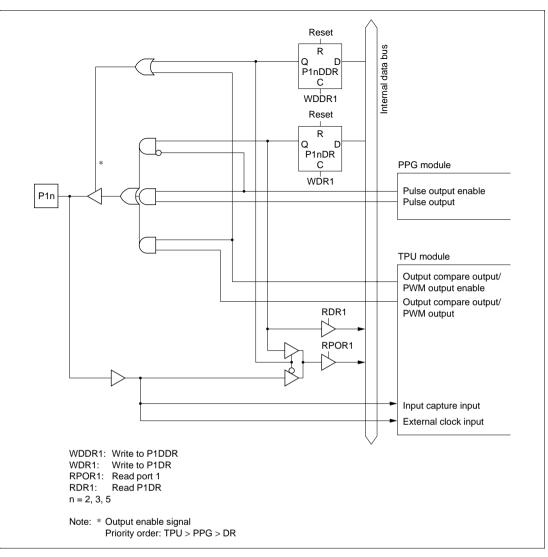

|      | 5.19.2   | Port 2                               | 30  |

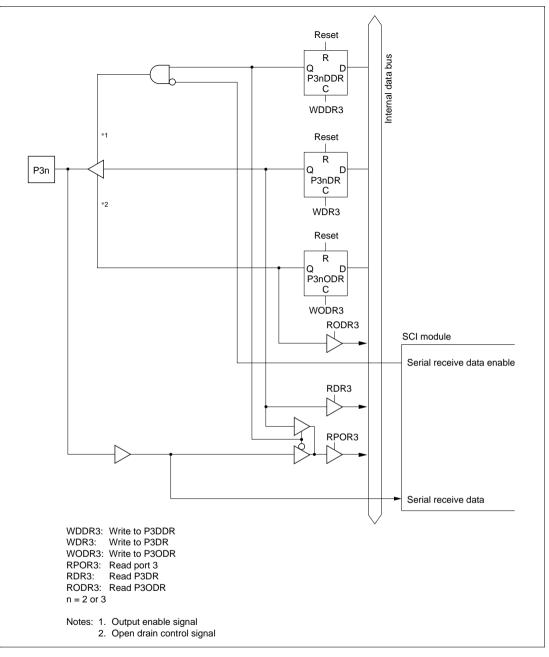

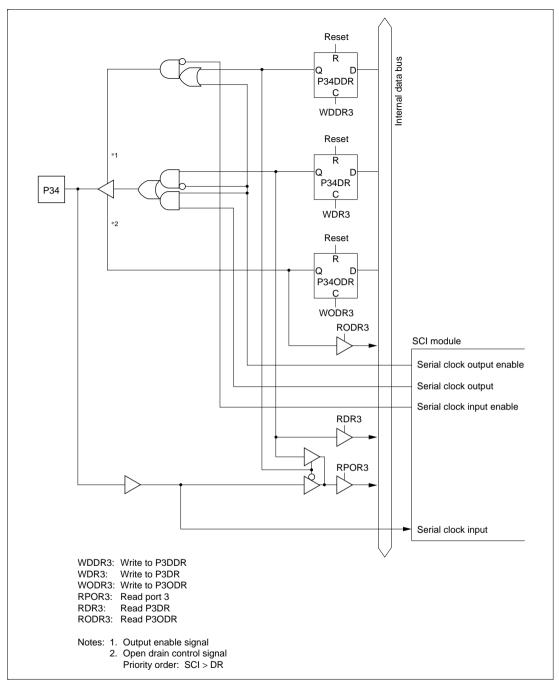

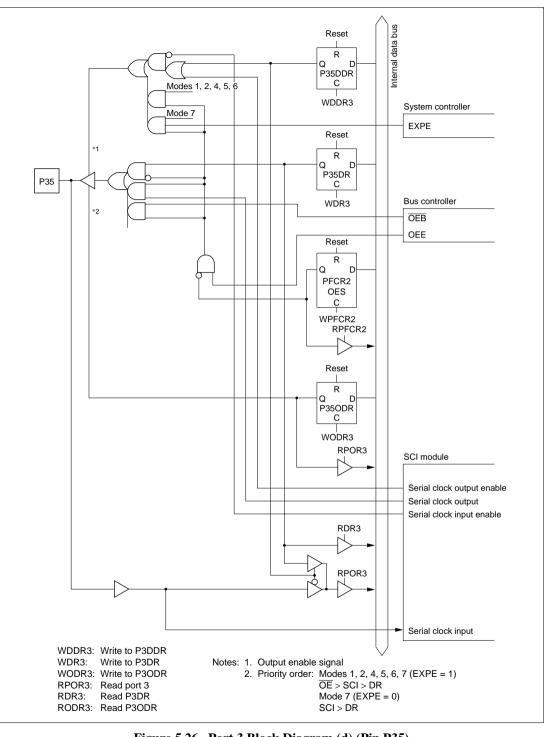

|      | 5.19.3   | Port 3                               | 303 |

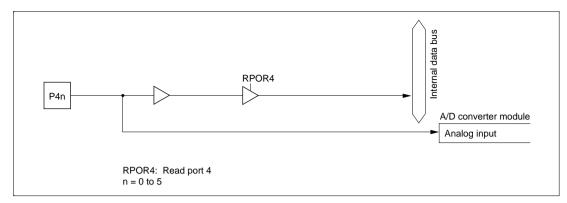

|      | 5.19.4   | Port 4                               | 30′ |

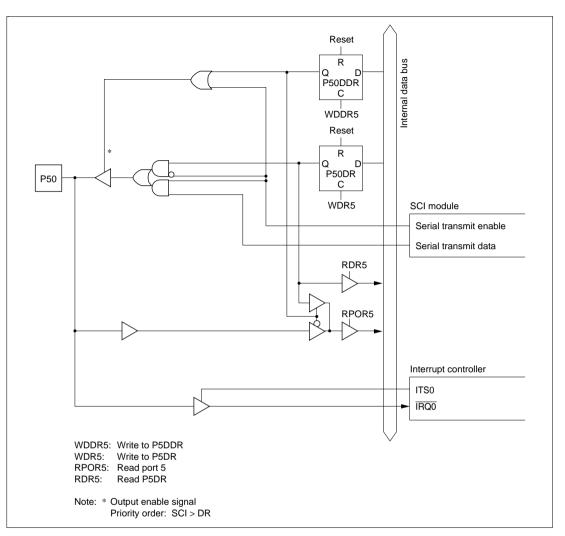

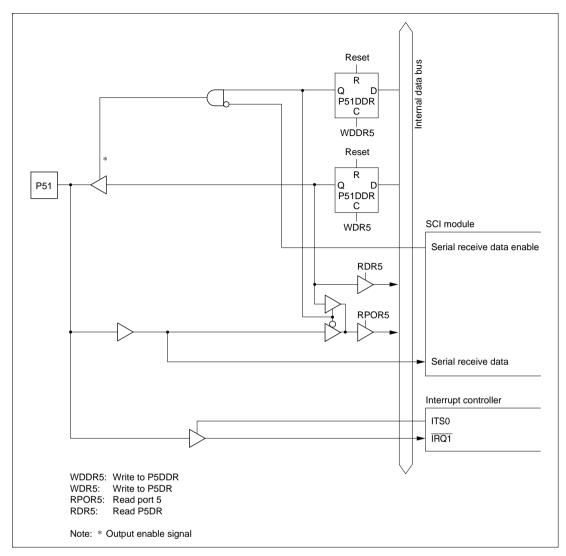

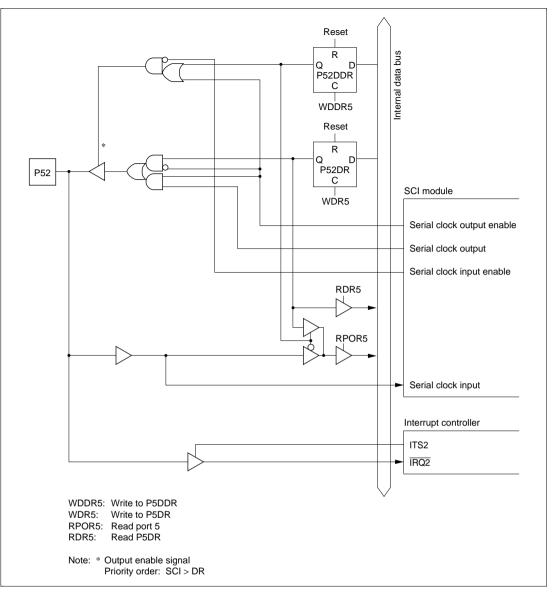

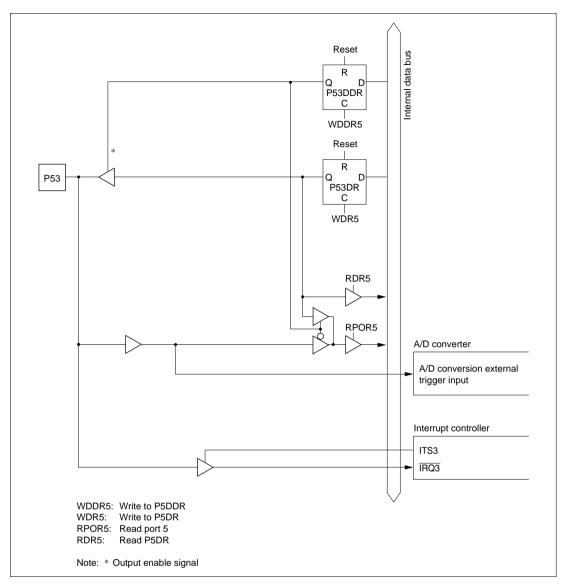

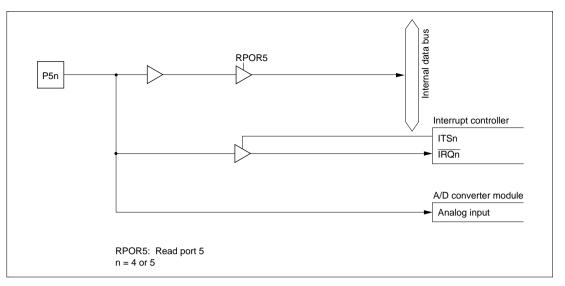

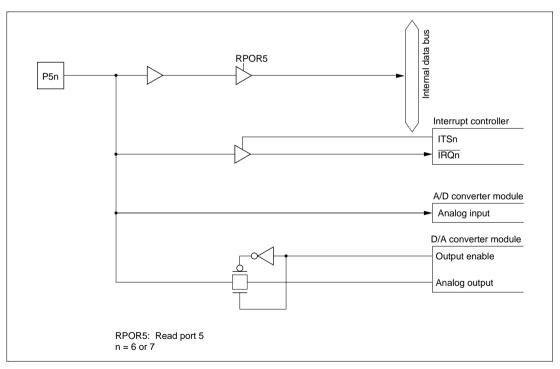

|      | 5.19.5   | Port 5                               | 308 |

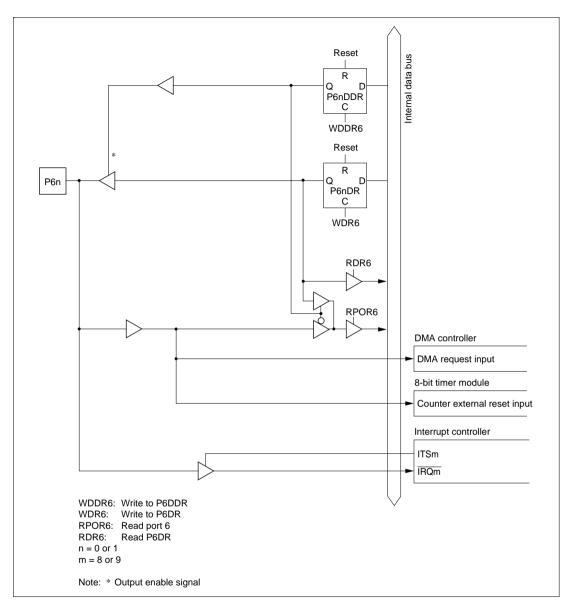

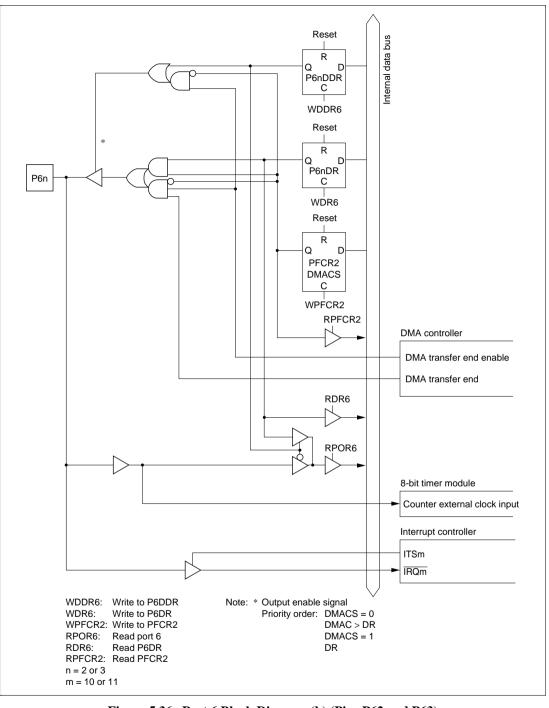

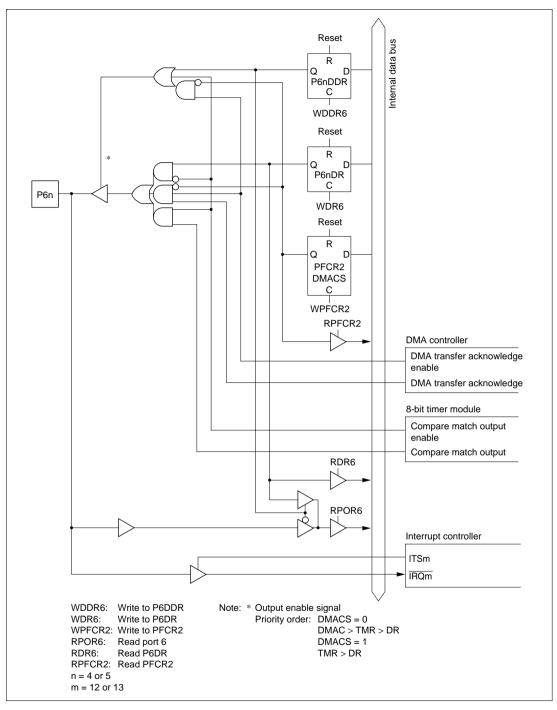

|      | 5.19.6   | Port 6                               | 313 |

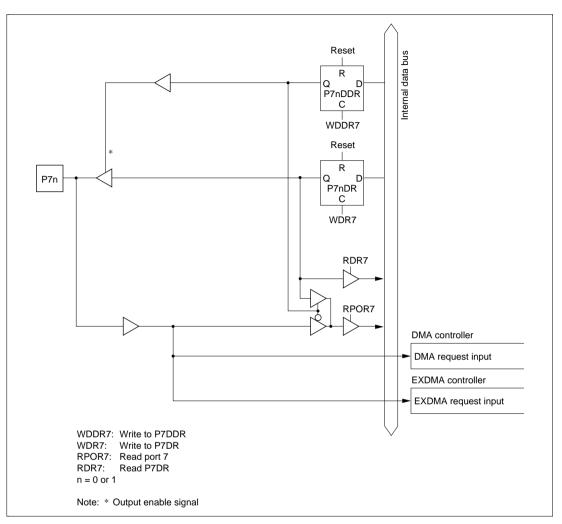

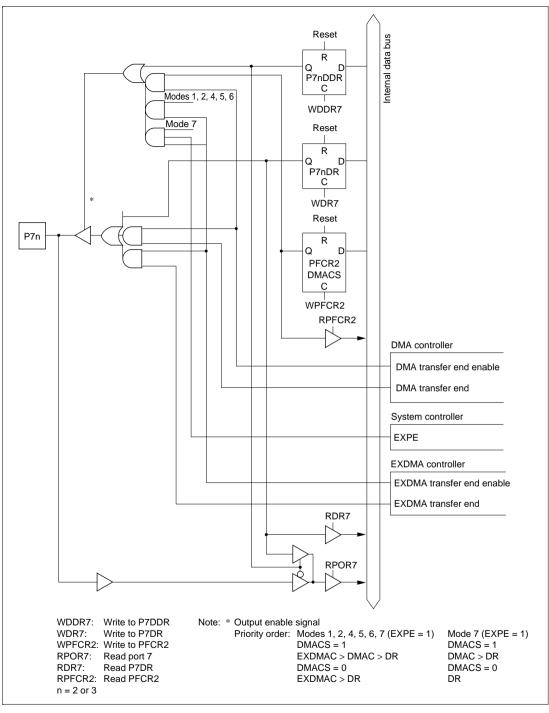

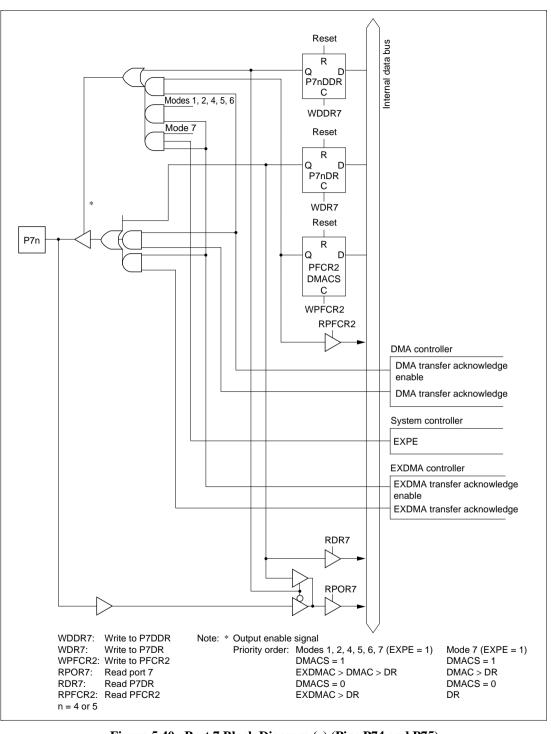

|      | 5.19.7   | Port 7                               | 310 |

|      | 5.19.8   | Port 8                               | 319 |

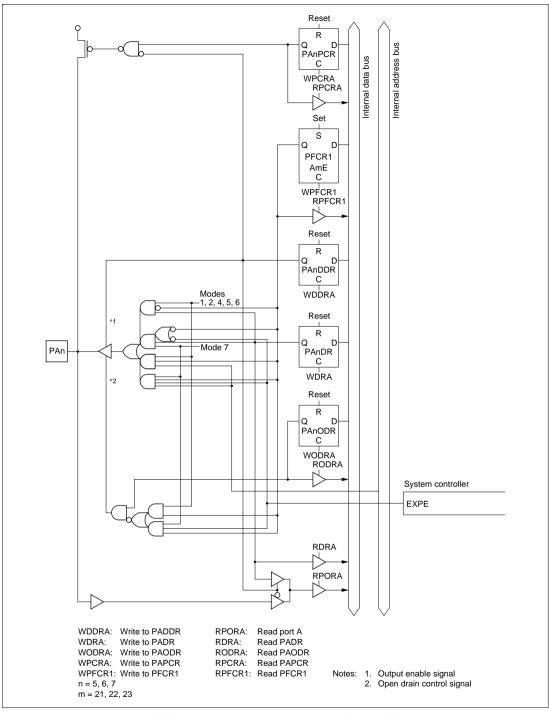

|      | 5.19.9   | Port A                               | 322 |

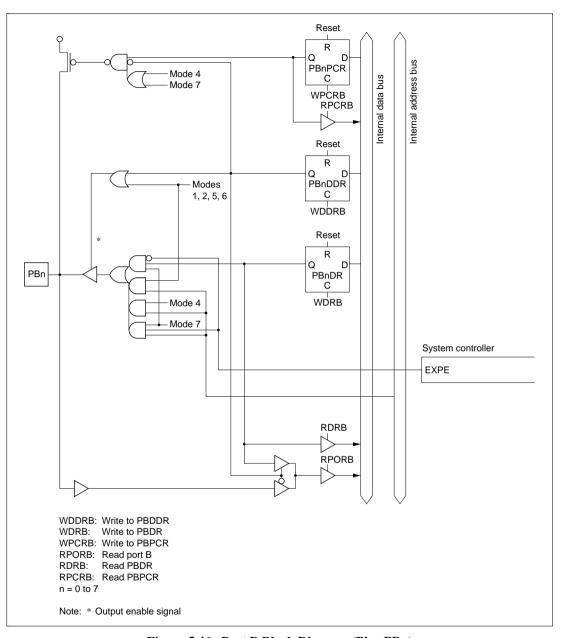

|      | 5.19.10  | Port B                               | 324 |

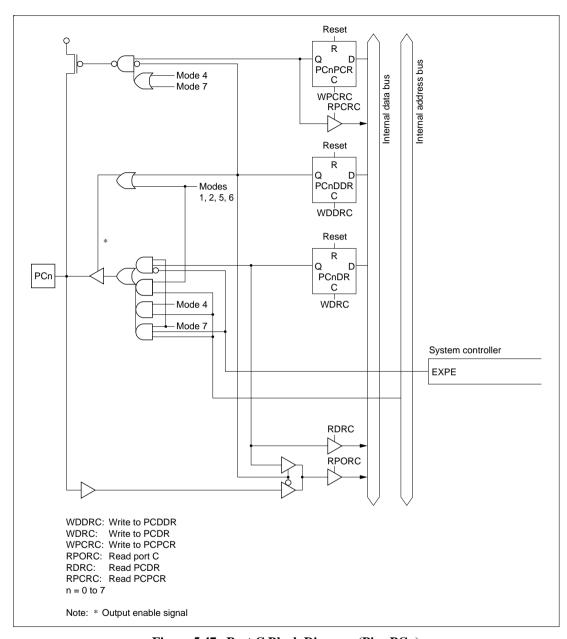

|      | 5.19.11  | Port C                               | 325 |

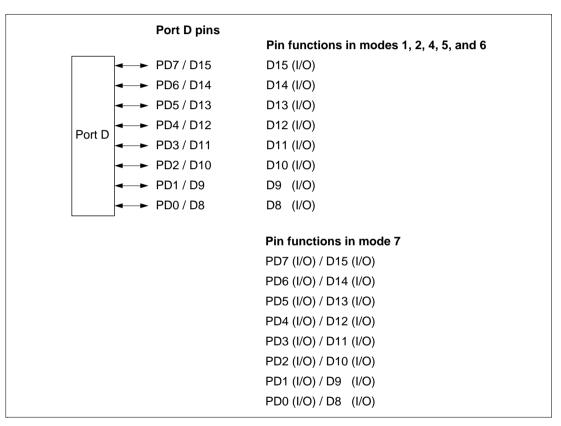

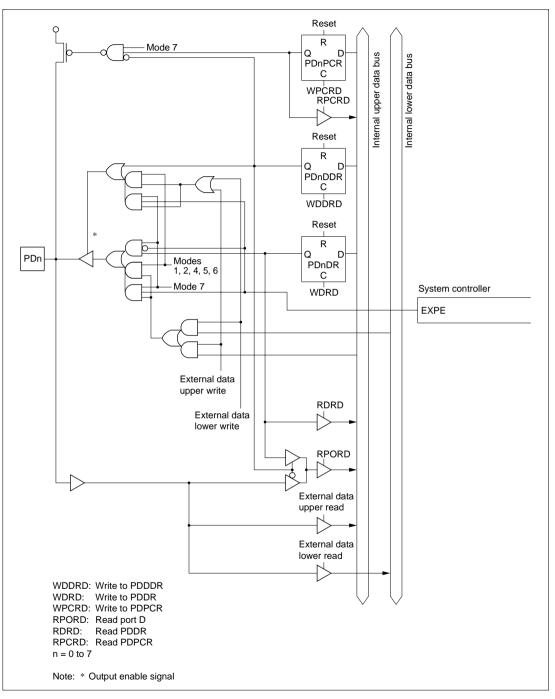

|      | 5.19.12  | Port D                               | 326 |

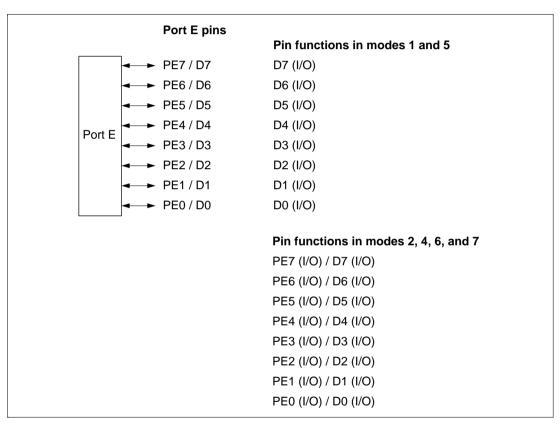

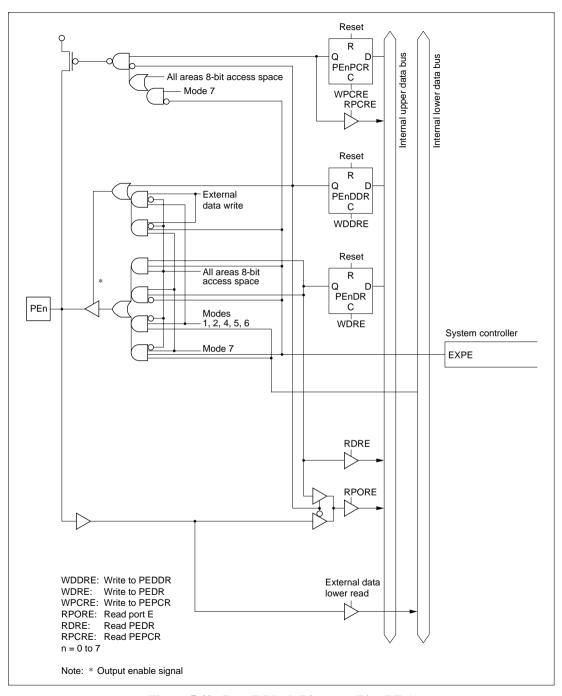

|      | 5.19.13  | Port E                               | 327 |

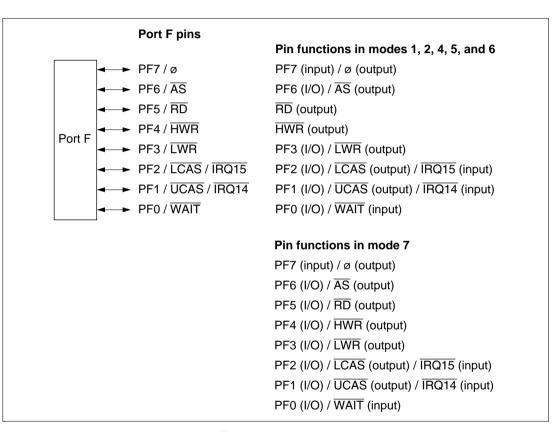

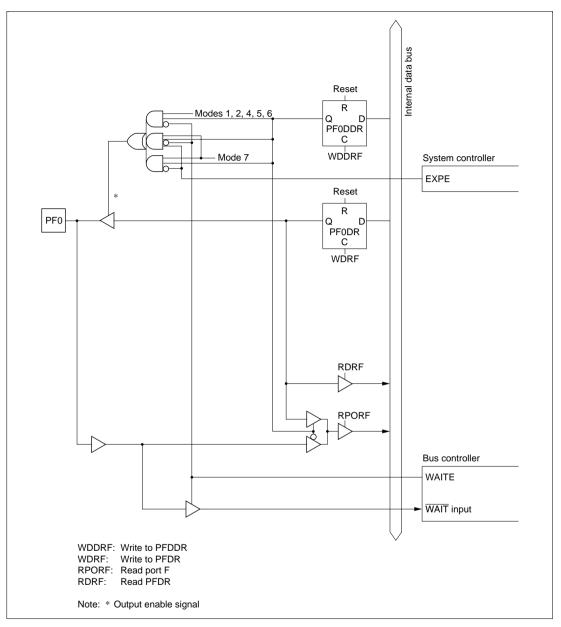

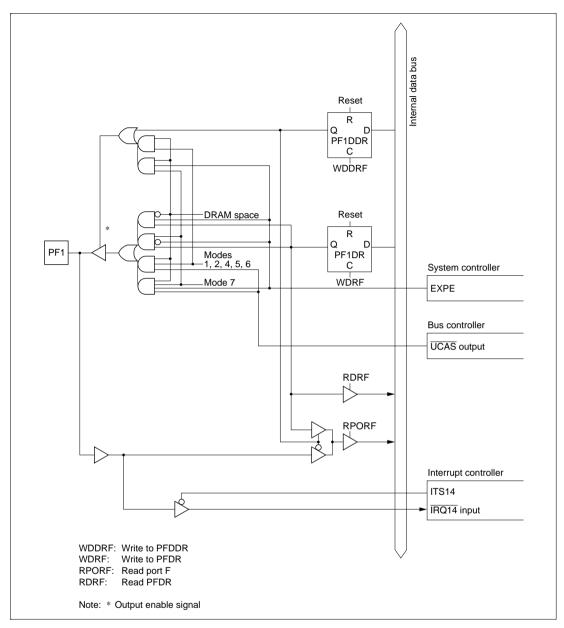

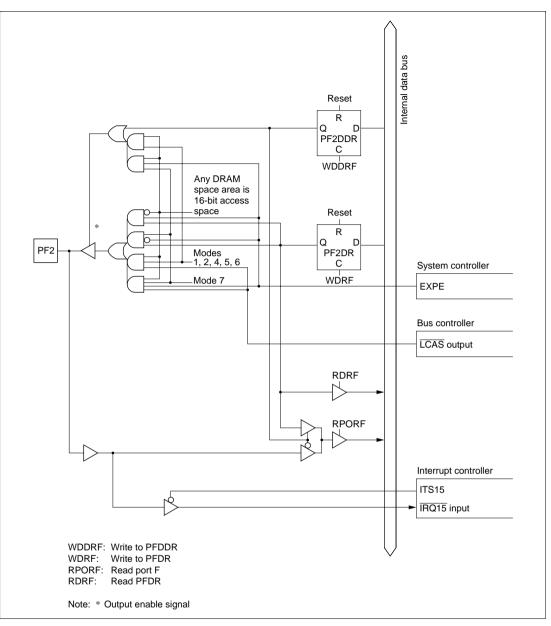

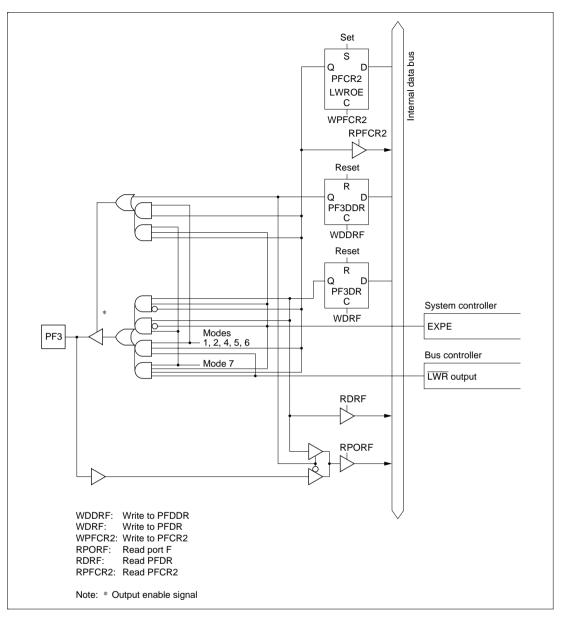

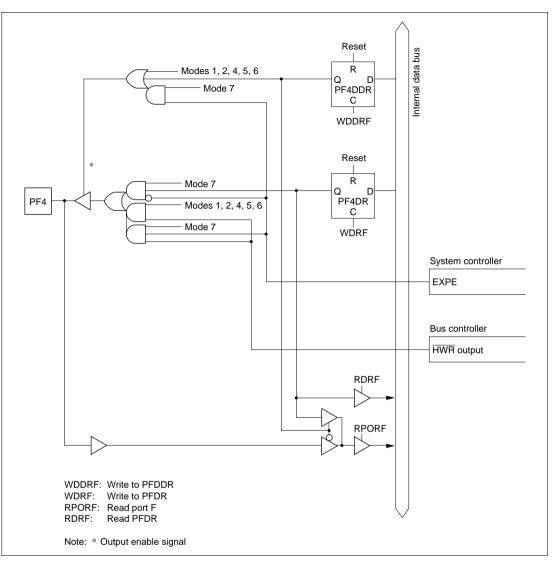

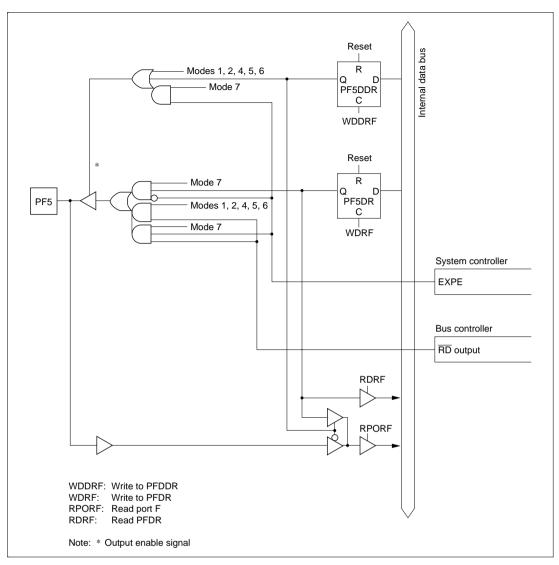

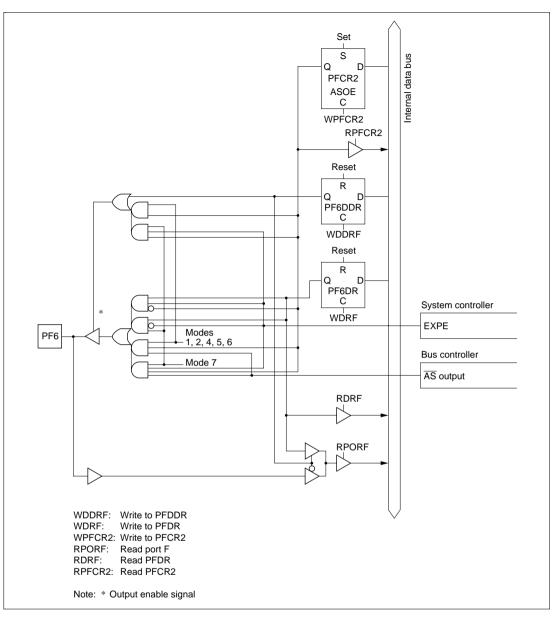

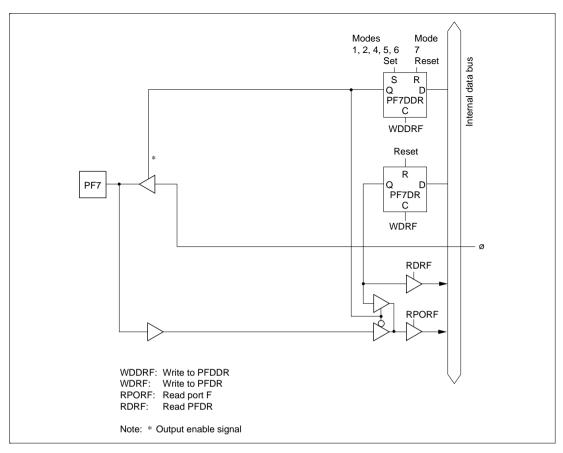

|      | 5.19.14  | Port F                               | 328 |

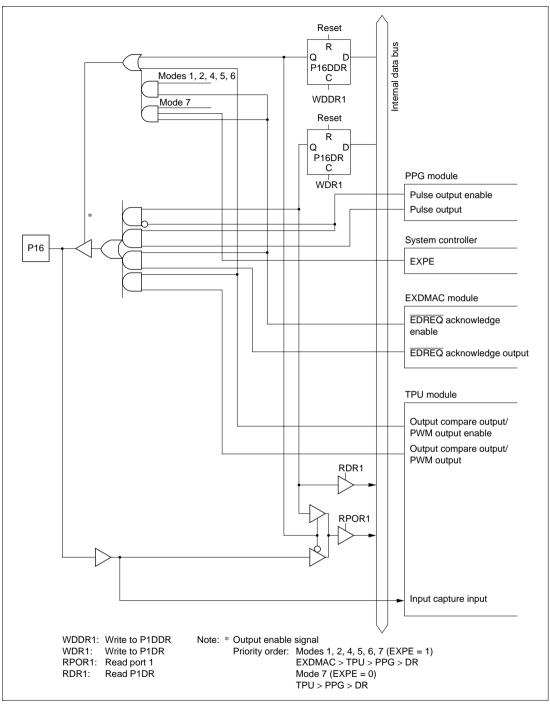

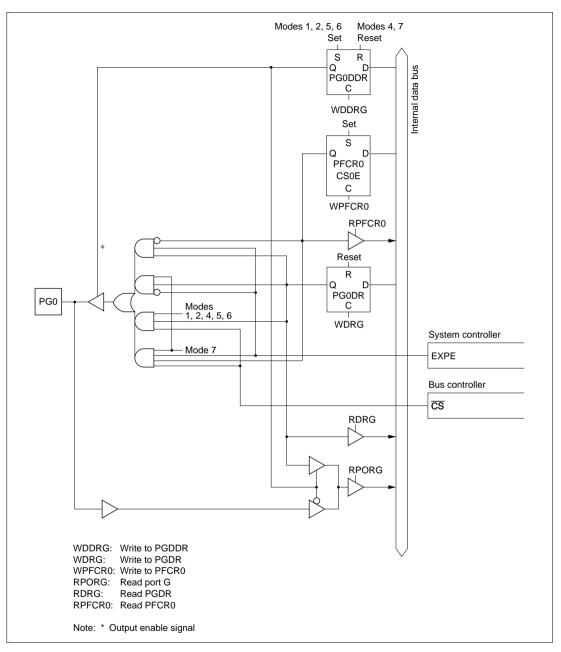

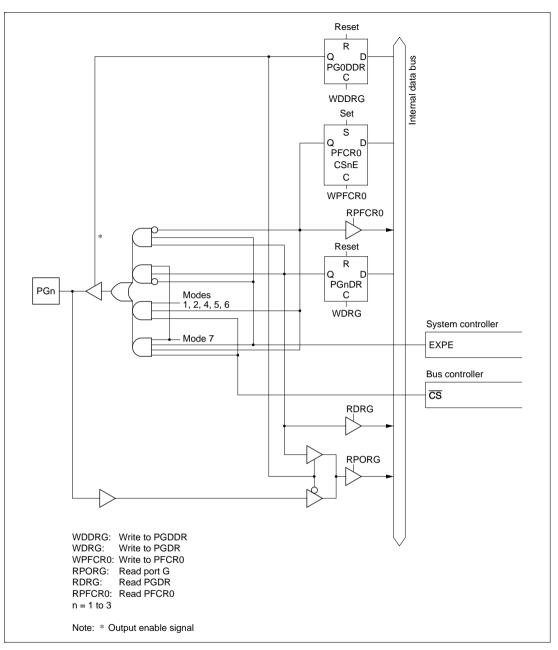

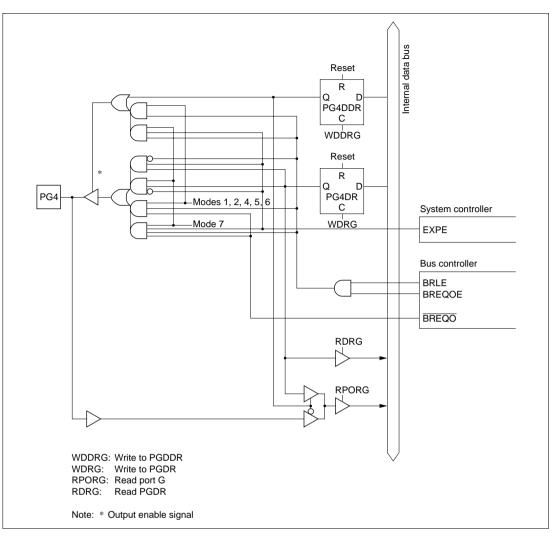

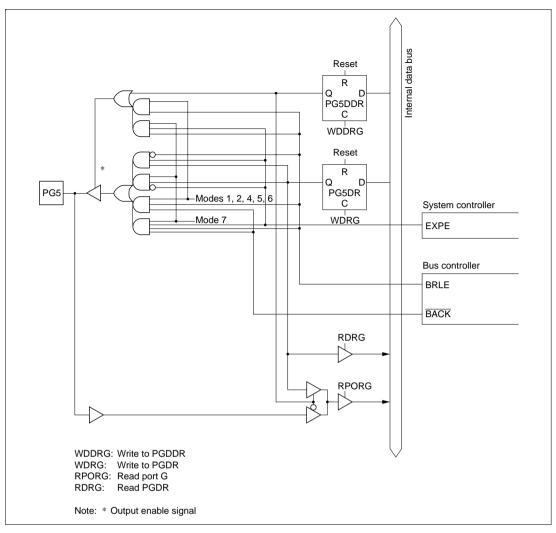

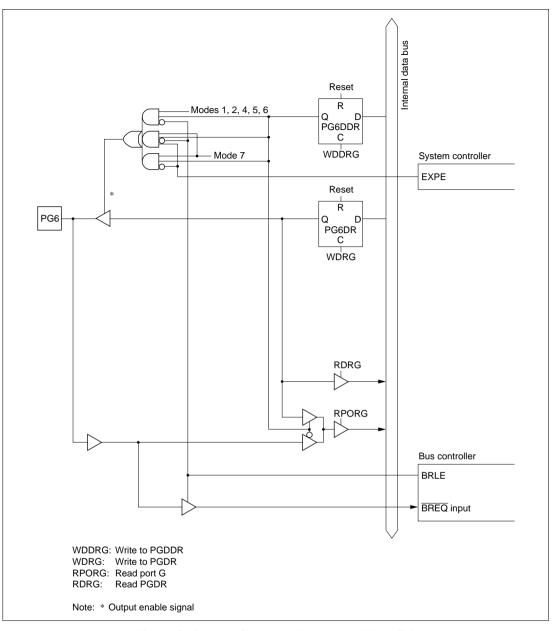

|      | 5.19.15  | Port G                               | 336 |

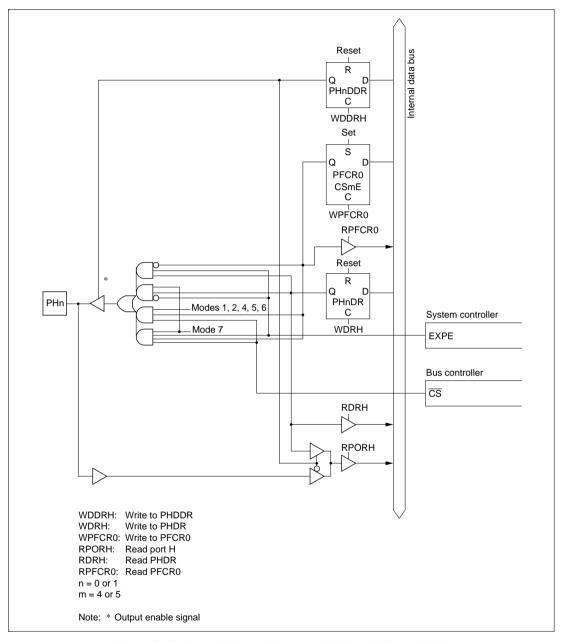

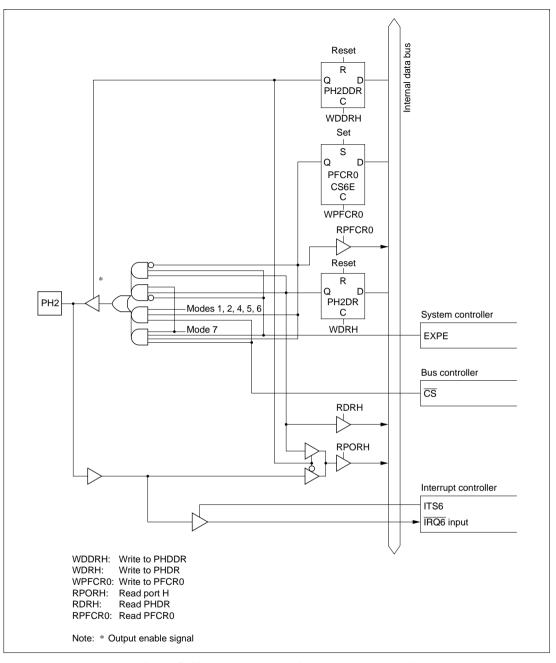

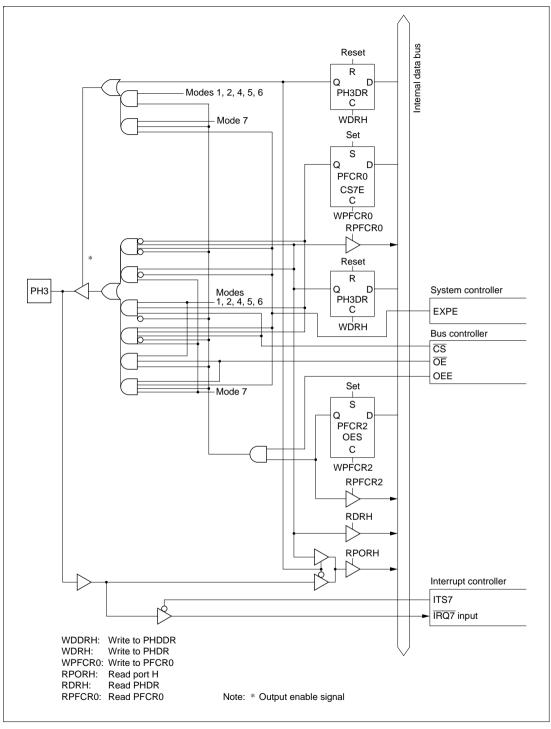

|      | 5.19.16  | Port H                               | 34  |

|      |          |                                      |     |

| Sect | ion 6    | Supporting Module Block Diagrams     | 345 |

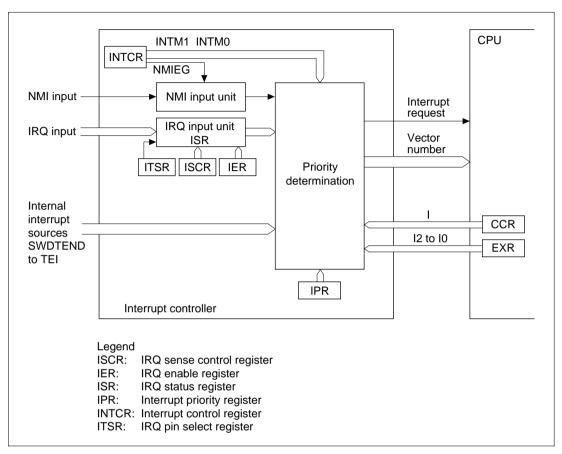

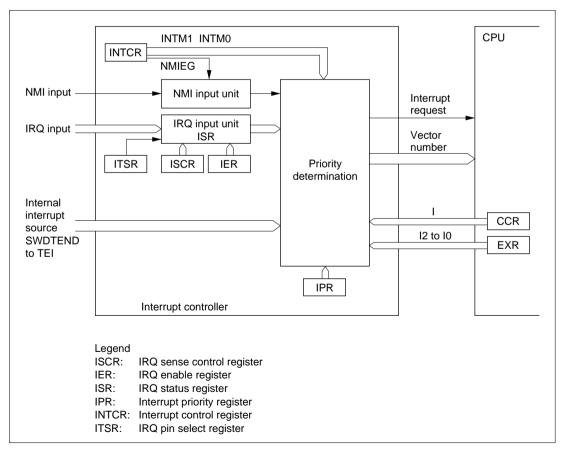

| 6.1  | Interrup | ot Controller                        | 345 |

|      | 6.1.1    | Features                             | 345 |

|      | 6.1.2    | Block Diagram                        | 345 |

|      | 6.1.3    | Pins                                 | 346 |

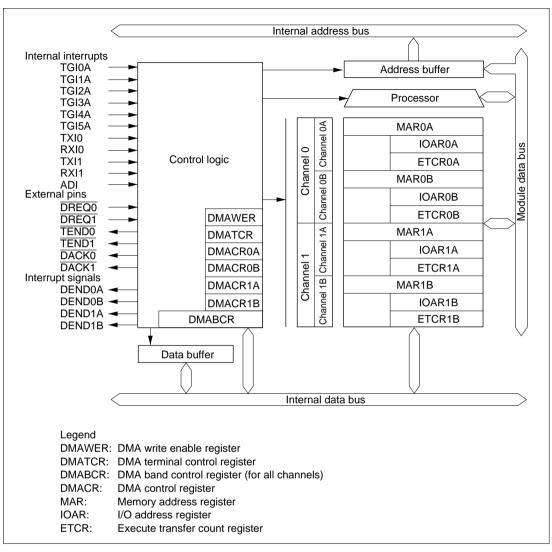

| 6.2  | DMA C    | Controller                           | 346 |

|      | 6.2.1    | Features                             | 346 |

|      | 6.2.2    | Block Diagram                        | 347 |

|      | 6.2.3    | Pins                                 | 348 |

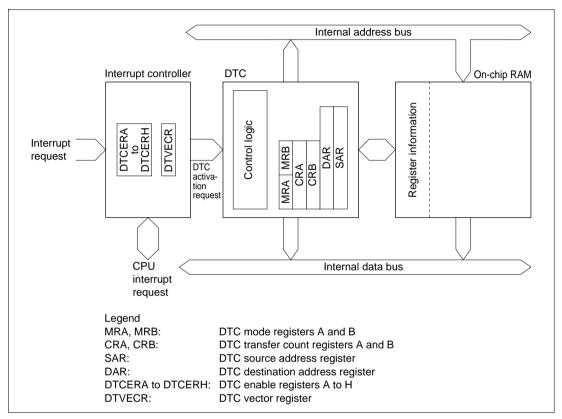

| 6.3  | Data Tr  | ansfer Controller                    | 348 |

|      | 6.3.1    | Features                             | 348 |

|      | 6.3.2    | Block Diagram                        | 349 |

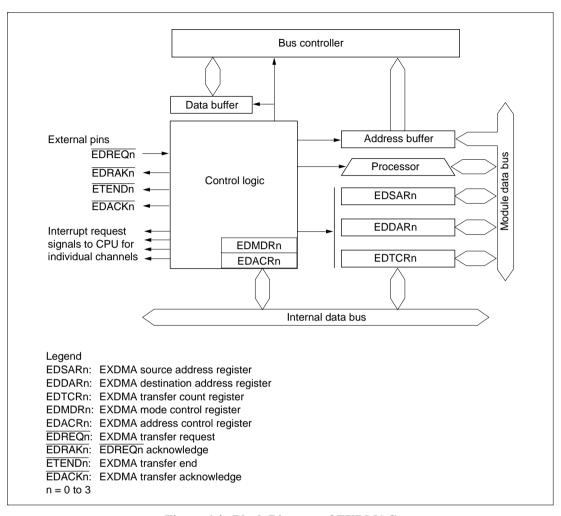

| 6.4  | EXDM.    | A Controller (EXDMAC)                | 350 |

|      | 6.4.1    | Features                             | 350 |

|      | 6.4.2    | Block Diagram                        | 35  |

|      |          | Pins                                 |     |

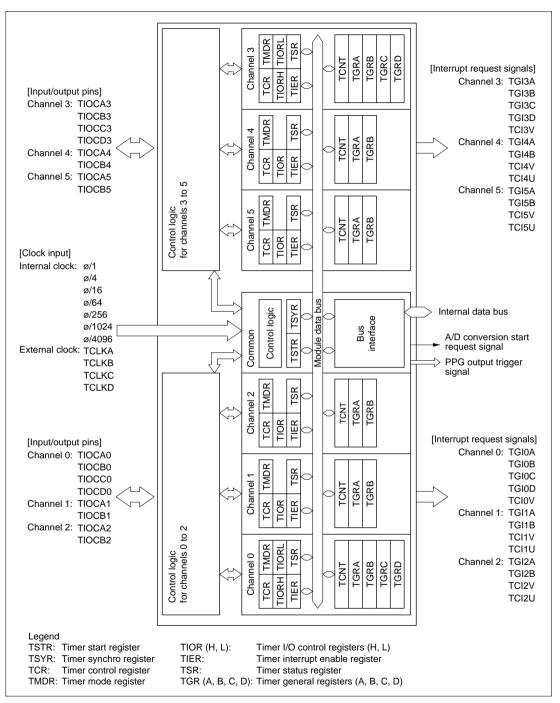

| 6.5  | 16-bit T | imer Pulse Unit                      | 353 |

|      | 6.5.1    | Features                             | 353 |

|      | 6.5.2    | Block Diagram                        | 354 |

|      | 6.5.3    | Pins                                 |     |

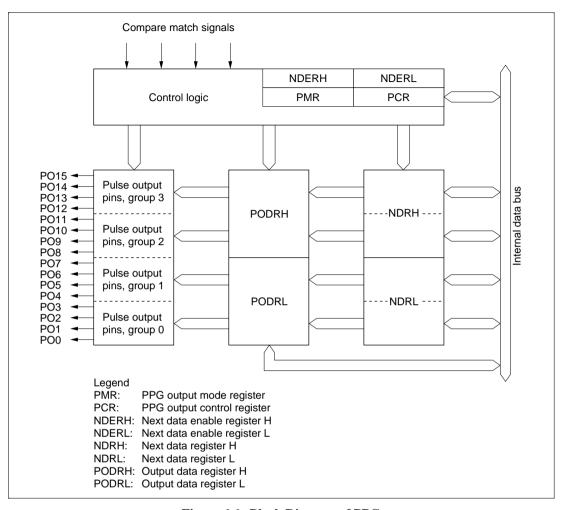

| 6.6  |          | nmable Pulse Generator               |     |

|      | _        | Features                             |     |

| vi   |          |                                      |     |

|      |          |                                      |     |

|      | 6.6.2    | Block Diagram                                                          | 357 |

|------|----------|------------------------------------------------------------------------|-----|

|      | 6.6.3    | Pins                                                                   | 358 |

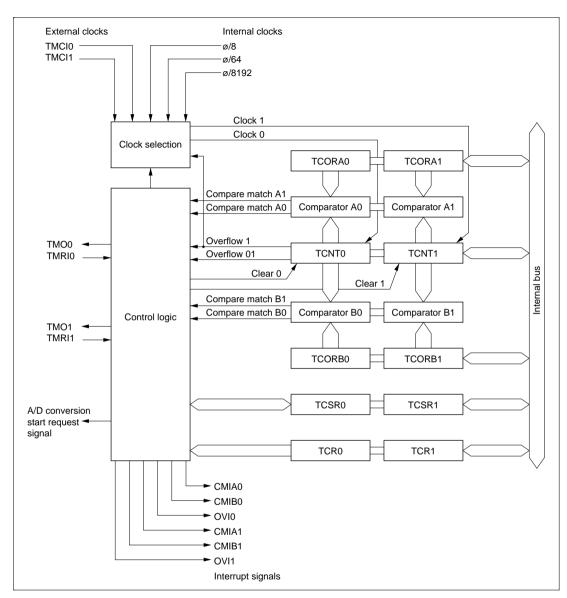

| 6.7  | 8-Bit T  | imer                                                                   | 358 |

|      | 6.7.1    | Features                                                               | 358 |

|      | 6.7.2    | Block Diagram                                                          | 359 |

|      | 6.7.3    | Pins                                                                   | 360 |

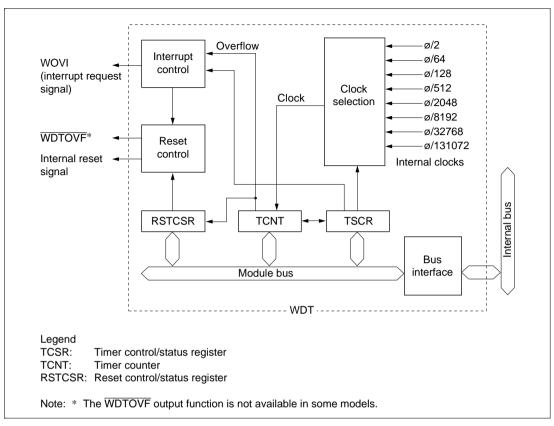

| 6.8  | Watch    | dog Timer                                                              | 360 |

|      | 6.8.1    | Features                                                               | 360 |

|      | 6.8.2    | Block Diagram                                                          | 361 |

|      | 6.8.3    | Pins                                                                   | 361 |

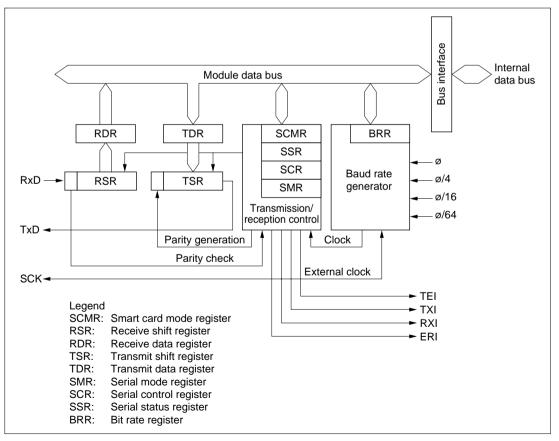

| 6.9  | Serial ( | Communication Interface                                                | 362 |

|      | 6.9.1    | Features                                                               | 362 |

|      | 6.9.2    | Block Diagram                                                          | 362 |

|      | 6.9.3    | Pins                                                                   | 363 |

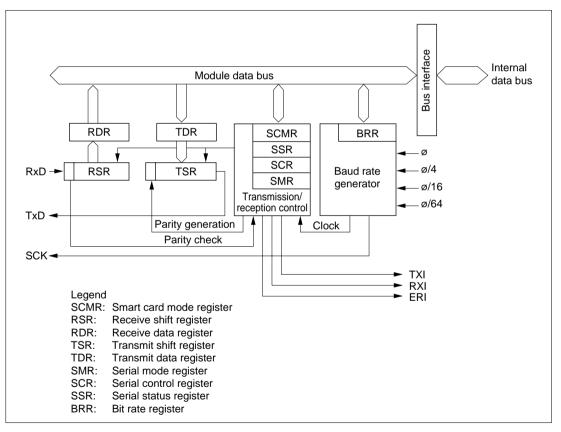

| 6.10 | Smart (  | Card Interface                                                         | 364 |

|      | 6.10.1   | Features                                                               | 364 |

|      | 6.10.2   | Block Diagram                                                          | 364 |

|      | 6.10.3   | Pins                                                                   | 365 |

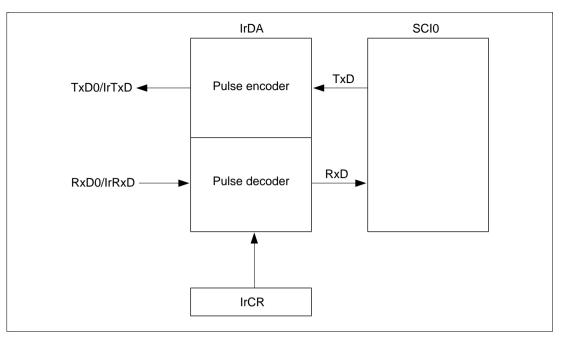

| 6.11 | IrDA     |                                                                        | 365 |

|      | 6.11.1   | Features                                                               | 365 |

|      | 6.11.2   | Block Diagram                                                          | 366 |

|      | 6.11.3   | Pins                                                                   | 366 |

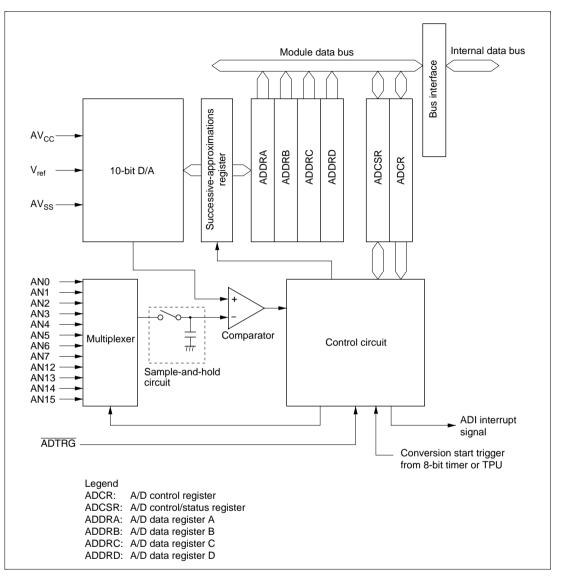

| 6.12 | A/D Co   | onverter                                                               | 367 |

|      | 6.12.1   | Features                                                               | 367 |

|      | 6.12.2   | Block Diagram                                                          | 368 |

|      | 6.12.3   | Pins                                                                   | 369 |

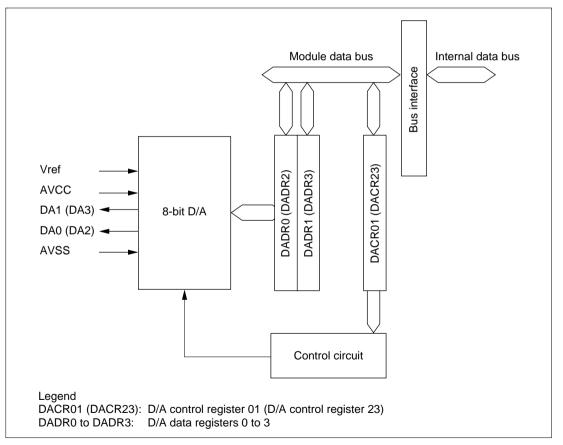

| 6.13 | D/A Co   | onverter                                                               | 370 |

|      | 6.13.1   | Features                                                               | 370 |

|      | 6.13.2   | Block Diagram                                                          | 370 |

|      | 6.13.3   | Pins                                                                   | 371 |

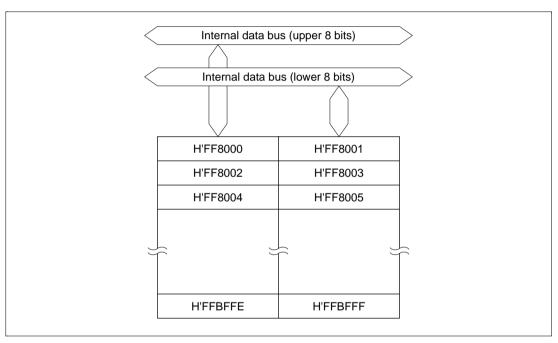

| 6.14 | RAM.     |                                                                        | 372 |

|      | 6.14.1   | Features                                                               | 372 |

|      | 6.14.2   | Block Diagram                                                          | 372 |

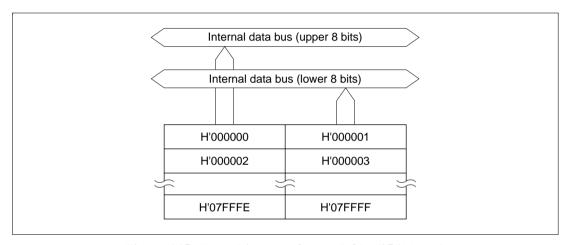

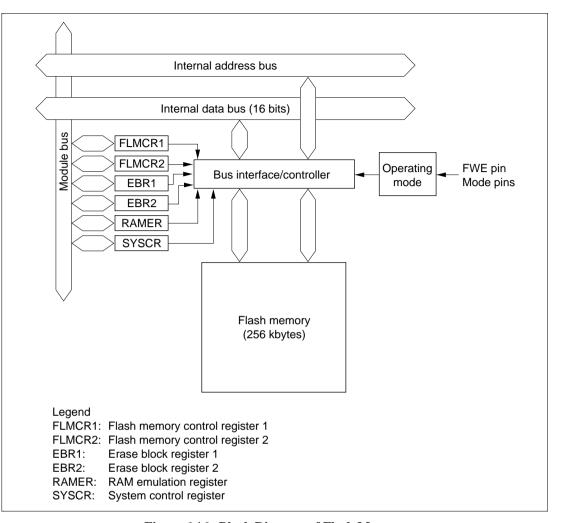

| 6.15 | ROM.     |                                                                        | 373 |

|      | 6.15.1   | Features                                                               | 373 |

|      | 6.15.2   | Block Diagrams                                                         | 373 |

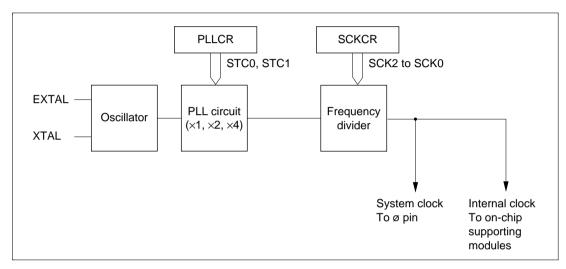

| 6.16 | Clock l  | Pulse Generator                                                        | 375 |

|      | 6.16.1   | Features                                                               | 375 |

|      | 6.16.2   | Block Diagram                                                          | 375 |

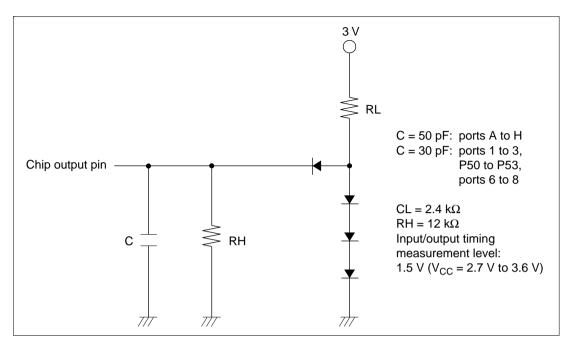

| Sect | ion 7    | Electrical Characteristics                                             | 377 |

| 7.1  | Electric | cal Characteristics of Mask ROM Version (H8S/2677, H8S/2676, H8S/2675, |     |

|      |          | 673) and ROMless Version (H8S/2670)                                    | 377 |

vii

|       | 7.1.1                 | Absolute Maximum Ratings                                   | 377 |  |  |  |  |  |

|-------|-----------------------|------------------------------------------------------------|-----|--|--|--|--|--|

|       | 7.1.2                 | DC Characteristics                                         | 378 |  |  |  |  |  |

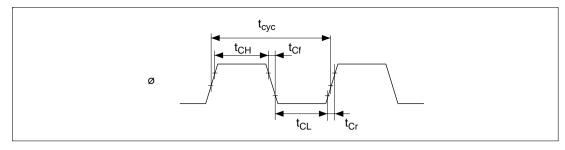

|       | 7.1.3                 | AC Characteristics                                         | 381 |  |  |  |  |  |

|       | 7.1.4                 | Conversion Characteristics                                 | 415 |  |  |  |  |  |

|       | 7.1.5                 | D/A Conversion Characteristics                             | 416 |  |  |  |  |  |

| 7.2   | Electric              | eal Characteristics of F-ZTAT Version (H8S/2677, H8S/2676) | 417 |  |  |  |  |  |

|       | 7.2.1                 | Absolute Maximum Ratings                                   | 417 |  |  |  |  |  |

|       | 7.2.2                 | DC Characteristics                                         | 418 |  |  |  |  |  |

|       | 7.2.3                 | AC Characteristics                                         | 421 |  |  |  |  |  |

|       | 7.2.4                 | A/D Conversion Characteristics                             | 430 |  |  |  |  |  |

|       | 7.2.5                 | D/A Conversion Characteristics                             | 431 |  |  |  |  |  |

|       | 7.2.6                 | Flash Memory Characteristics                               | 432 |  |  |  |  |  |

| 7.3   | Usage l               | Note                                                       | 434 |  |  |  |  |  |

| Secti | on 8                  | Registers                                                  | 435 |  |  |  |  |  |

| 8.1   | List of               | Registers (Address Order)                                  |     |  |  |  |  |  |

| 8.2   |                       | Registers (By Module)                                      |     |  |  |  |  |  |

| 8.3   | Register Descriptions |                                                            |     |  |  |  |  |  |

#### Section 1 Overview

#### 1.1 Overview

The H8S/2678 Series comprises microcomputers (MCUs), built around the H8S/2600 CPU, employing Hitachi's original architecture, and equipped with on-chip supporting functions necessary for system configuration.

The H8S/2600 CPU has an internal 32-bit architecture, is provided with sixteen 16-bit general registers and a concise, optimized instruction set designed for high-speed operation, and can address a 16-Mbyte linear address space. The instruction set is upward-compatible with H8/300 and H8/300H CPU instructions at the object-code level, facilitating migration from the H8/300, H8/300L, or H8/300H Series.

On-chip supporting functions required for system configuration include direct memory access controller (DMAC), EXDMA controller (EXDMAC), and data transfer controller (DTC) bus masters, ROM and RAM memory, a16-bit timer pulse unit (TPU), programmable pulse generator (PPG), 8-bit timer module (TMR), watchdog timer module (WDT), serial communication interfaces (SCI, IrDA), A/D converter, D/A converter, and I/O ports.

A high-functionality bus controller is also provided, enabling fast and easy connection of DRAM and other kinds of memory.

The on-chip ROM is either single-power-supply flash memory (F-ZTAT<sup>TM\*</sup>) or mask ROM, enabling users to respond quickly and flexibly to changing application specifications, growing production volumes, and other conditions. The ROM is connected to the CPU via a 16-bit data bus, enabling both byte and word data to be accessed in one state. Instruction fetching is thus speeded up, and processing speed increased.

The features of the H8S/2678 Series are shown in table 1.1.

Note: \* F-ZTAT is a trademark of Hitachi, Ltd.

#### Table 1.1 Overview

| Item                  | Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU                   | General-register architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                       | <ul> <li>Sixteen 16-bit general registers (also usable as sixteen 8-bit registers<br/>or eight 32-bit registers)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                       | High-speed operation suitable for realtime control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                       | <ul> <li>Maximum operating frequency: 33 MHz</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                       | High-speed arithmetic operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                       | 8/16/32-bit register-register add/subtract: 30 ns (33 MHz operation)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                       | $16 \times 16$ -bit register-register multiply: 90 ns (33 MHz operation)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                       | 32 ÷ 16-bit register-register divide: 600 ns (33 MHz operation)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                       | Instruction set suitable for high-speed operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                       | <ul> <li>— Sixty-five basic instructions</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                       | <ul> <li>8/16/32-bit transfer/arithmetic and logic instructions</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                       | <ul> <li>Unsigned/signed multiply and divide instructions</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                       | <ul> <li>Powerful bit-manipulation instructions</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                       | CPU operating mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

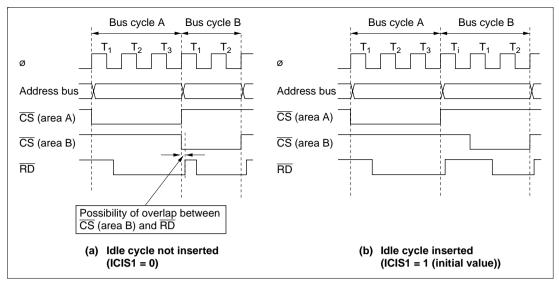

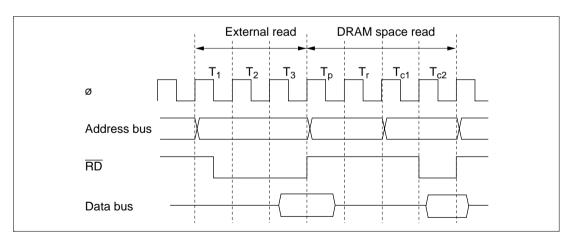

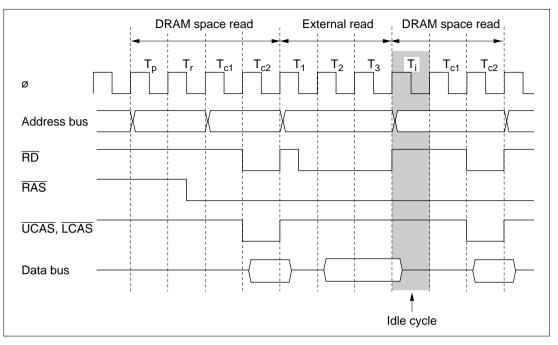

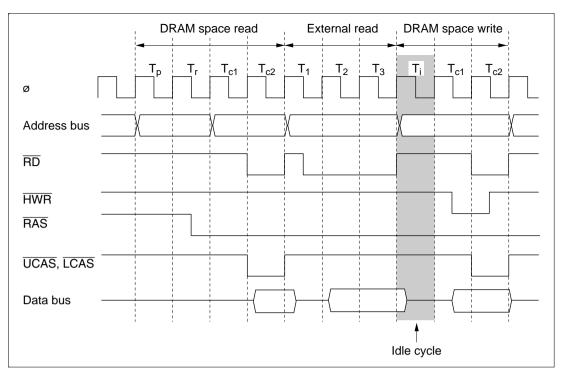

|                       | <ul> <li>Advanced mode: 16-Mbyte address space</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |